[TOC]

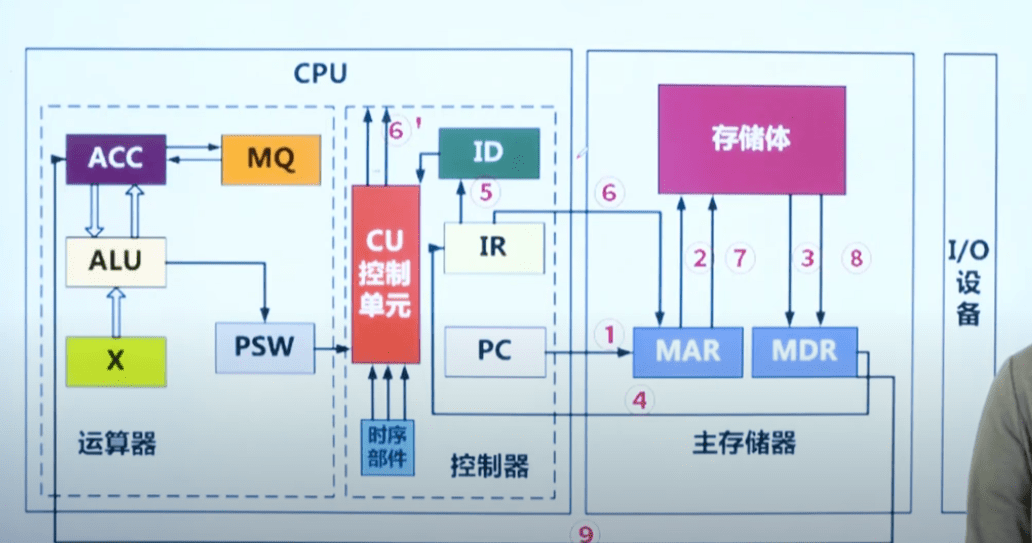

## 硬件图

### CPU 部分

#### 运算器:

* **ACC(累加器-Accumulator)**:

* 是 CPU 中的一个寄存器,临时存储算术或逻辑运算的中间结果。

* 运算完成后结果通常保存在 ACC 中。

* **MQ(乘商寄存器-Multiplier Quotient Register)**:

* 用于乘法和除法操作中存储乘数或商/余数。

* **ALU(算术逻辑单元-Arithmetic Logic Unit)**:

* 执行算术运算(如加减乘除)和逻辑运算(如与、或、非)。

* **X (寄存器-Index Register)**:

* 通常用于与 ALU 协作,参与运算,辅助存储一个操作数。

* **PSW(程序状态字-Program Status Word)**:

* 记录程序执行状态,比如零标志、进位标志、溢出标志等。

* * *

#### 控制器:

* **CU(控制单元-Control Unit)**:

* 产生控制信号,协调各部分工作流程。

* 依据指令内容发出操作指令,控制数据在 CPU、内存、I/O 之间流动。

* **IR(指令寄存器-Instruction Register)**:

* 存储当前正在执行的那条指令。

* **ID(指令译码器-Instruction Decoder)**:

* 对 IR 中的指令进行译码,交由 CU 决定具体操作。

* **PC(程序计数器-Program Counter)**:

* 存放下一条要执行的指令的地址,每执行一条指令就加 1。

* 实现程序的自动顺序执行。

* **时序部件**:

* 控制不同阶段(如取指、译码、执行)信号的时序与节奏

### 主存储器部分:

* **存储体**:

* 实际存储程序指令和数据的区域(RAM 内存)。

* CPU 从这里读取指令和数据。

* **MAR(内存地址寄存器-Memory Address Register)**:

* 用于指定要访问的内存地址。

* 由 PC 或 CU 送入指令或数据的地址。

* **MDR(内存数据寄存器-Memory Data Register)**:

* 用于临时存放从内存中读出的数据或将要写入内存的数据。

### I/O设备(输入输出):

* 外围设备的数据输入输出,可通过 MDR 等寄存器进行数据传输。

### 数据流编号解析

| 编号 | 含义 |

| -- | -------------------- |

| 1 | PC → MAR:将指令地址送入 MAR |

| 2 | MAR → 内存:访问内存获取指令 |

| 3 | 指令 → MDR:从内存中取出的指令 |

| 4 | MDR → IR:将指令送入 IR |

| 5 | IR → ID:指令译码 |

| 6 | 控制信号发出,执行相关操作 |

| 7 | 数据访问(如读取数据操作) |

| 8 | 数据写入内存(如写操作) |

| 9 | I/O 设备读写(可与 MDR 通信) |

## cpu硬件组成

### 运算器的组成包含如下:

1. **算术逻辑单元 ALU**: 数据的算术运算和逻辑运算;

2. **累加寄存器 AC**: 通用寄存器,为 ALU 提供一个工作区,用来暂存数据;

3. **数据缓冲寄存器 DR**: 写内存时,暂存指令或数据;

4. **状态条件寄存器 PSW**: 存状态标志与控制标志。

* * *

### 控制器的组成包含如下:

1. **程序计数器 PC**: 存储下一条要执行指令的地址;处理器首先需要从PC中取出指令在内存中的地址,通过地址总线址获取。

2. **指令寄存器 IR**: 存储即将执行的指令;

3. **指令译码器 ID**: 对指令中的操作码字段进行分析解释;

4. **地址寄存器 AR**: 用来保存当前 CPU 所访问的内存单元的地址;

5. **时序部件**: 提供时序控制信号。

## 主存

**存储器**的基本单位是存储单元,一般以8位二进制为一个存储单元。每个存储单元都有一个地址,一般用十六进制数表示。

## 数据总线

* **数据总线(Data Bus)**:

* 用途:传输实际的数据(如操作数、计算结果)。

* 特点:双向传输,宽度(如8位、32位、64位)决定一次能传输的数据量。例如,64位数据总线可同时传输64位数据。

* 示例:CPU与内存交换运算结果时使用数据总线。

* **地址总线(Address Bus)**:

* 用途:传输内存地址或I/O设备地址,指定数据存储或读取的位置。

* 特点:单向传输(通常由CPU发出),宽度决定寻址范围。例如,32位地址总线可寻址2^32(4GB)内存。

* 示例:CPU通过地址总线告诉内存读取或写入的具体地址。

* **控制总线(Control Bus)**:

* 用途:传输控制信号,协调系统各部分的运行(如读/写信号、中断信号、时钟信号)。

* 特点:信号种类多样,单向或双向,具体信号取决于系统设计。

* 示例:CPU发送“读”信号到内存,触发数据读取操作。

按总线数据线的多少分为并行总线和串行总线

| 特性 | 并行总线 | 串行总线 |

| --- | --- | --- |

| **数据线数量** | 多条(如8、16、32条) | 单条或少数几条(如1-4条) |

| **传输方式** | 同时传输多位 | 按序传输单比特 |

| **带宽** | 依赖宽度和频率 | 依赖频率和通道数 |

| **布线复杂度** | 高,占用空间大 | 低,布线简单 |

| **抗干扰性** | 易受串扰影响 | 差分信号,抗干扰强 |

| **频率限制** | 高频下信号同步困难 | 支持更高频率 |

| **典型应用** | 早期PCI、并行ATA | PCIe、USB、SATA |

## 存储器

按照所处位置分类:

- **内存(主存)**:CPU 当前使用的指令和数据;

- **外存(辅存)**:存放程序和数据。

按照构成材料分类:

- **半导体存储器**:双极结电路器件;

- **磁存储器**:依靠电流上磁存储信息,主存;

- **光存储器**:利用光学两种不同的状态长期保存信息,外存。

按照工作方式分类:

- **读/写存储器**:如 RAM。

- **只读存储器**(ROM):用户不能写入数据。

- 可擦写的只读存储器:PROM(用户可写入一次)。

- 可编程的只读存储器:EPROM(可多次编程,紫外线擦除)。

- 电可擦写的只读存储器:EEPROM(可多次编程,电擦除)。

- 可编程的只读存储器:擦近 EEPROM,U 盘。

按照访问方式分类:

- **顺序存储器**(如磁带);

- **随机存储器**(如 RAM)。

- **直接存储器**(如 DAM)。

- **相对存储器**(如硬盘,Cache)。

按照寻址方式分类

- **随机存储器RAM**:按地址访问存储器的任一单元,主存

- **顺序存储器SAM**:方问时按顺序查找目标地址,磁带

- **直接存储器DAM**:按数据块所在位置方问,磁盘

- **相联存储器**:按照内容进行访问,如何CPU Cache

分类

- **速度从快到慢**: 寄存器->cache->主存->磁盘

- **容量从小到大**: 寄存器->cache->主存->磁盘

- **价格从高到低**: 寄存器->cache->主存->磁盘

## 校验码

信息保存在电容中,如遇电磁环境干扰,会导致电容的充放电或触发器的翻转,存在存储器的信息可能会出错

类型

- 奇偶校验码

- 海明码

- 循环冗余校验码(CRC)

码距

- 在一个码组内为了检测e个误码,要求最小码距应该满足:

d>=e+1 (为了检测一个误码,最少为2)

- 在一个码组内为了纠正t个误码,要求最小码距应该满足:

d>=2t+1 (为了纠正一个误码,最少为3)

- 同时纠错检错:d>=e+t+1

### 奇偶校验码

**奇偶效验码例子**

在原始数据后加上一位 校验位,使得整个数据的“1”的个数变成:

- 偶校验(Even Parity):偶数个 1

- 奇校验(Odd Parity):奇数个 1

示例:使用偶校验

**正确例子**

1. 原始数据(4 位):

```

1011 (3 个 1)

```

2. 为变成偶数个 1 → 加个校验位 1:

```

1011 1(共 4 个 1,是偶数)

```

3. 接收端校验:

如果接收到的数据中“1”的个数不是偶数 ⇒ 说明有错误。

**出错例子**

- 接收方收到:

```

1001 1(共 3 个 1,是奇数)

```

发现不是偶数 ⇒ 说明出错,但 不能定位是哪一位错了,只能检测错误

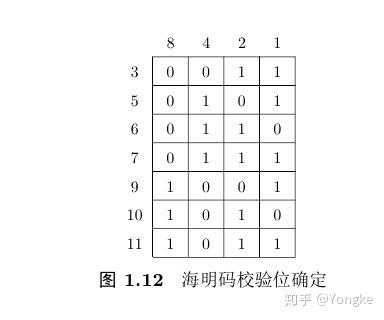

### 海明码

- 海明码是奇偶效验码和分组码组成

已知原始数据为1001011,采用Hamming Code编码后,求实际发送的数据?

1. 计算需要的校验位数目。从题目中可知数据为的长度为7,即`m=7`,带入公式`$ m + k + 1 \leq 2^k

$`

可等`k>=4`最小值为4,最后实际发送的数据长度为`7+4=11`,根据海明码原则组合排列7为数据和4位校验码`$ 1 = 2^0, 2 = 2^1, 4 = 2^2, 8 = 2^3

$`

列表中数是格子数是左侧是指的二进制码

计算海明码, 是否是奇数,计算方式是表格中列中为1的值

```

a1=X3⊕X5⊕X7⊕X9⊕X11=1⊕0⊕1⊕0⊕1=1

a2=X3⊕X6⊕X7⊕X10⊕X11=1⊕0⊕1⊕1⊕1=0

a3=X5⊕X6⊕X7=0⊕0⊕1=1

a4=X9⊕X10⊕X11=0⊕1⊕1=0

```

得到新的11位数为10110010011

**海明码纠错**

如果接收端收到的数据10110110011,接收方需要先计算校验位的值,计算的值再和数据中的校验位进行异或比较

监督公式如下

```

h1=X3⊕X5⊕X7⊕X9⊕X11⊕a1=X3⊕X5⊕X7⊕X9⊕X11⊕X1

h2=X3⊕X6⊕X7⊕X10⊕X11⊕a=X3⊕X6⊕X7⊕X10⊕X11⊕X2

h3=X5⊕X6⊕X7⊕a3=X5⊕X6⊕X7⊕X3

h4=X9⊕X10⊕X11⊕a4=X9⊕X10⊕X11⊕X4

```

计算的本意是接收端重新计算一次校验码,然后和数据中校验码进行比较。如果自己计算的校验码和数据中的校验码相同,记为0,不同则记为1

计算结果按照 `$ h_{4} h_{3} h_{2} h_{1} $`的顺序进行排列,如果结果等于0说明数据没有出错;如果结果不等于0,说明数据出错,把该数据转 化为10进制数,就是出错数据的位置,因为二进制数中每一位置只有2种状态,0或者1。因此知道错误的位置后,改正错误就非常简单,把对应的数据取反即可

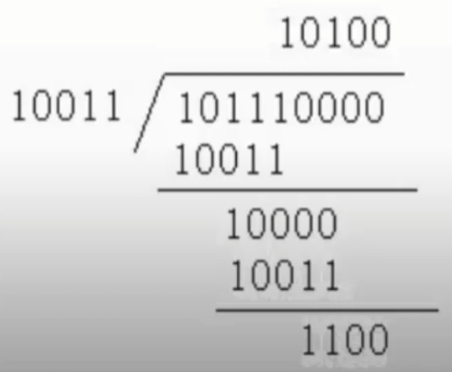

### 循环冗余校验码

CRC 是把数据看作一个二进制多项式,通过“模一个固定多项式”来计算出一个校验码,用于发现数据是否被篡改或损坏。

- 只能检测错误,**不能纠正**。

- 比奇偶校验和简单的校验和算法更强大,能检测到突发错误(如多个连续比特翻转)。

- 算法简单、硬件实现容易,常用在以太网、USB、文件压缩、磁盘校验等地方。

| CRC 名称 | 多项式(十六进制) | 用途 |

| ---------- | ------------ | -------------------- |

| CRC-4 | `0x07` | SMBus,ATM头部 |

| CRC-8 | `0x07` | SMBus,ATM头部 |

| CRC-16-IBM | `0x8005` | Modbus,XMODEM |

| CRC-32 | `0x04C11DB7` | Ethernet,ZIP文件,PNG图片 |

**示例**

### 举个简单例子(CRC-4)

假设:

* 数据:`10111`

* 生成 CRC-4多项式:`10011`(对应多项式:x⁴ + x + 1=`$ 1x^{4} +0x^{3} +0x^{2} +1x^{1} +1 $`=10011)

**步骤如下:**

1. **数据末尾补零:**

补零的个数 = 生成多项式的位数 - 1 = 4

所以补 4 个 0,数据变成:`101110000`

2. **进行模2除法(异或运算):**

用 `10011` 去“除”上面的数据(本质上是异或)

3. **最终得到的余数就是 CRC 校验码,。** 结果为 1100

**注意**: 余数必须比除数少且只少一位,不够就前面补0

4. **将余数添加到原始数据末尾,一起发送。**

接收端也用相同的方式做除法,如果最后余数为 0,则数据无误;否则说明有错误。

## 指令

### 顺序方式

各条机器指令之间顺序串行地执行,执行完一条指令后才取下一条指令。缺点是速度慢,机器各部件利用率低。

### 重叠方式

在解释第K条指令的操作完成之前就可以开始解释第K+1条指令。

### 指令流水技术

指令步骤的并行、提高处理器执行指令的效率。假设使用流水线将指令流的处理过程划分为取指、分析、执行三个并行处理的过程段。在这个流水线中,处理器有三个操作部件,同时对这三条指令进行加工,加快了程序的执行速度。几乎所有的高性能计算机都采用了指令流水线。

**流水线的周期**

为取指、分析、执行三段中**最长的一端**当中流水线的周期即`$ \triangle t $`

理论公式(考试重点) `$ (t1+t2+...+tk)+(n-1)*\triangle t $`

实践公式 `$ (k+n-1)+(n-1)*\triangle t $`

**示例**

例如:若流水线把一条指令分为取指、分析和执行三个部分,三部分的时间分别是取指2ns,分析2ns,执行1ns。那么流水线周期是多少?100条指令全部执行完毕需要的时间是多少?

**那么流水线周期是多少:**

解:取最大的时间,即2ns

**100条指令全部执行完毕需要的时间是多少?**

解: 根据理论公式`t1...tk`为 `(2+2+1)`三段一共为5ns,然后在加上`(100-1)`等于99 乘以流水线周期为2ns,一共为203

### 流水线的吞吐率和最大吞吐率

**流水线的吞吐率和最大吞吐率**:吞吐率是指单位内流水线处理机流出的结果数。对指令而言,就是单位时间内执行的指令数。

吞吐率: `$ TP=\frac{指令条数}{流水线执行时间} $`

最大吞吐率 `$ TP_{max} =\frac{1}{\triangle t} $`

流水线加速比:`$ S=\frac{不使用流水线的时间}{使用流水线执行时间} $`,不使用流水线时间就是顺讯执行指令的时间

## 高速缓冲存储器

是为了解决:解决CPU和主存之间的速度差异,避免CPU“空等”现象。

局部性原理:

- **时间局部性**

是指如果一个数据(或程序指令)在某一时刻被访问过,那么在不久的将来,它可能会再次被访问。换句话说,程序在某个时间点访问的数据可能会在短时间内再次被访问。如CPU 缓存和for等循环的优化

- **空间局部性**

是指如果程序访问了某个存储位置,那么它可能会访问该存储位置附近的数据。例如,当一个数据项被访问时,紧邻的内存地址的数据也很可能会在接下来的操作中被访问。如数组访问和内存页的访问当读取数组或内存页时,会提前把附近的数据缓存

### cache 映射方法

- 直接映射

- 直接映像方式的优点是地址变换很简单,如何Cache 中的第0页就是主存中的第0页,依此类处,

- 缺点是不灵活,**块冲突率高**。

- 全相联映射

- 主存中的任何一页都可以映射到Cache中的任何一页

- 位置不受限制,十分灵活。其主要缺点是无法从主存块号中直接获得 Cachel的块号,变换比较复杂,速度比较慢。

- 组相联映像

- 距离CPU较近位置可以采用直接映像或者组相联映像距离CPU较远的可以采用全相联映像

### cache 性能

**读Cache**

CPU在访问内存时,首先判断所要访问的内容是否在Cache中,如果在,就称为"命中”,此时CPU直接从Cache中调用该内容;否则,就称为“不命中”,CPU只好去内存中调用所需的子程序或指令了。

如果以`Hc`为代表对Cache的访问命中率,`tc`为Cache的存取时间,`tm`为主存的访问时间,则Cache的平均访问时间ta为 `ta=Hctc+(1-Hc)tm`,即命中的时间+不明中的时间

<br/>

**写Cache**

因为Cache的内容是部分主存内容的副本,应该与主存内容保持一致。而CPU对cache的写入更改了cache内容,如何与主存内容保持一致就有几种写操作工作方式可供选择,统称为**写策略**。

1. 写回法(write-back)

当CPU对cache写命中时,只修改cache的内容不立即写入主存,只当此行被换出时才写回主存。这种策略使cache在CPU-主存之间,不仅在读方向而且在写方向上都起到高速缓存作用。

2. 写直达法

又称全写法,写透。是当cache写命中时,cache与主存同时发生写修改。

3. 标记法

数据进入Cachel后,有效位置1,当cpu对该数据修改时,数据只写入主存并将该有效位置0。要从cache中读取数据时要测试其有效位,若为1则直接从cache中取数,否则从主存中取数。

### Cache 替换算法

1. 随机算法

这是最简单的替换算法。随机法完全不管Cache块过去、现在及将来的使用情况,简单地根据一个随机数,选择一块替换掉。

2. 先进先出(First In and First Out,FIFO)算法

按调入Cache的先后决定淘汰的顺序,即在需要更新时,将最先进入Cache的块作为被替换的块。这种方法要求为每块做一记录,记下它们进入Cache的先后次序。这种方法容易实现,而且系统开销小。其缺点是可能会把一些需要经常使用的程序块(如循环程序)替换掉。

3. 近期最少使用(Least Recently Used,LRU)算法

LRU算法是把 CPU近期最少使用的块作为被替换的块。这种替换方法需要随时记录Cache中各块的使用情况,以便确定哪个块是近期最少使用的块。LRU算法相对合理但实现起来比较复杂,系统开销较大。通常需要对每一块设置一个称为“年龄计数器”的硬件或软件计数器,用以记录其被使用的情况。

4. 最不经常使用页置换(Least Frequently Used,LFU)算法

要求在页置换时置换引用计数最小的页,因为经常使用的页应该有一个较大的引用次数。但是有些页在开始时使用次数很多,但以后就不再使用,这类页将会长时间留在内存中,因此可以将引用计数寄存器定时右移一位,形成指数衰减的平均使用次数。LFU的复杂度以及计数器规模都L比LRU大,LRU只关注近期访问情况,而LFU会统计累计访问次数作为淘汰的依据。该算法计数器位数多,实现困难

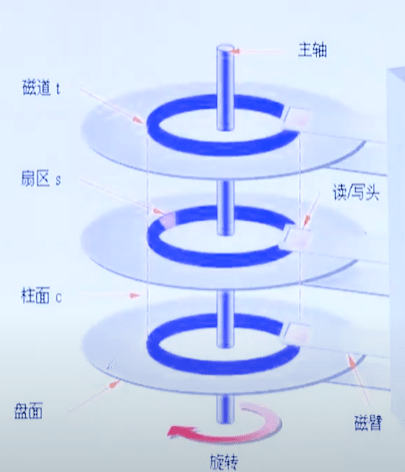

## 磁盘存储器

常用的外存有磁带存储器、硬盘存储器、磁盘阵列和光盘存储器。

**磁盘存储器**

其中:n为保存数据的总记录面数, t为每面磁道数,S为每道的扇区数, b为每个扇区存储的字节数。硬盘存取时间:

存储容量=`n×t×s×b`

硬盘存取时间=`寻道时间+等待时间+读/写时间其中读/写时间`可忽略不计,平均寻道时间+平均等待时间

## 指令系统

Flynn 分类

根据指令流和数据流的多倍性特分类

1. 指令流:指机器执行的指令序列:

2. 数据流:指由指令流调用的数据序列,包括输入数据和中间结果,但不包括输出数据。

分成四类

1. **单指令流单数据流**

(Single Instruction stream and Single Datastream,SISD):SISD其实就是传统的顺序执行的单处理器计算机,其指令部件每次只对一条指令进行译码,并只对一个操作部件分配数据。

2. **单指令流多数据流**

(Single Instruction stream and Multiple

Data stream,SIMD):SIMD以并行处理机(矩阵处理机)为代表,并行处理机包括多个重复的处理单元,由单一指令部件控制,按照同一指令流要求为它们分配各自所需的不同数据。

3. **多指令流单数据流**

(Multiple Instruction stream and Single

Data stream,MISD):MISD具有n个处理单元,按n条不同指令的要求对同一数据流及其中间结果进行不同的处理。一个处理单元的输出又作为另一个处理单元的输入。这类系统实际上很少见到。

4. **多指令流多数据流**

(Multiple Instruction stream and Multiple

Data stream,MIMD):MIMD是指能实现作业、任务、指令等各级全面并行的多机系统。如多核处理器、多处理机属于MIMD。

### 复杂指令

复杂指令系统CISC的特点

1. 指令数量众多。指令系统拥有大量的指令,通常有100~250条。

2. 指令使用频率相差悬殊。最常使用的是一些比较简单的指令,仅占指令总数的20%,但在程序中出现的频率却占80%。而大部分复杂指令却很少使用。

3. 支持很多种寻址方式。支持的寻址方式通常为5~20种。

4. 变长的指令。指令长度不是固定的,变长的指令增加指令译码电路的复杂性

5. 指令可以对主存单元中的数据直接进行处理。典型的CISC通常都有指令能够直接对主存单元中的数据进行处理,其执行速度较慢。

6. 以微程序控制为主。CISC的指令系统很复杂,难以用硬布线逻辑(组合逻辑)电路实现控制器,通常采用微程序控制。

### 简单指令集

1. 指令数量少。优先选取使用频率最高的一些简单指令和一些常用指令,避免使用复杂指令。只提供了LOAD(从存储器中读数)和STORE(把数据写入存储器)两条指令对存储器操作,其余所有的操作都在CPU的寄存器之间进行。

2. 指令的寻址方式少。通常只支持寄存器寻址方式、立即数寻址方式和相对寻址方式。

3. 指令长度固定,指令格式种类少。因为RISC指令数量少、格式少

相对简单,其指令长度固定,指令之间各字段的划分比较一致,译码相对容易

4. 以硬布线逻辑控制为主。为了提高操作的执行速度,通常采用硬布线逻辑(组合逻辑)来构建控制器。

5. 单周期指令执行,采用流水线技术。因为简化了指令系统,很容易利用流水线技术,使得大部分指令都能在一个机器周期内完成。少数指令可能会需要多周期,例如,LOAD/STORE指令因为需要访问存储器,其执行时间就会长一些。

6. 优化的编译器:RISC的精简指令集使编译工作简单化。因为指令长度固定、格式少、寻址方式少,编译时不必在具有相似功能的许多指令中进行选择,也不必为寻址方式的选择而费心,同时易于实现优化,从而可以生成效率执行的机器代码。

7. CPU中的通用寄存器数量多,一般在32个以上,有的可达上干

## 磁盘阵列

创建类型

* **RAID 0(条带化)**

* **特点**:数据分割后并行写入多个磁盘,提升读写速度,无冗余。

* **优点**:性能高,适合需要快速读写的场景(如视频编辑)。

* **缺点**:一个磁盘故障,数据全损,适合非关键数据存储。

* **适用场景**:高性能需求,无需数据保护。

* **RAID 1(镜像)**

* **特点**:数据同时写入两个或多个磁盘,互为镜像,提供冗余。

* **优点**:高可靠性,一个磁盘故障不影响数据。

* **缺点**:存储效率低(仅50%),成本高。

* **适用场景**:关键数据存储,如数据库或服务器。

* **RAID 5(分布式奇偶校验)**

* **特点**:数据和奇偶校验信息分布在至少三个磁盘上,允许一个磁盘故障。

* **优点**:兼顾性能和冗余,存储效率较高。

* **缺点**:重建数据耗时,写入性能稍低于RAID 0。,磁盘容量 N-1

* **适用场景**:企业存储、中小型服务器。

* **RAID 6(双奇偶校验)**

* **特点**:类似RAID 5,但有两个奇偶校验,可容忍两个磁盘故障。

* **优点**:更高冗余,适合大型存储系统。

* **缺点**:需要至少四个磁盘,写入性能略低。磁盘容量 N-2

* **适用场景**:高可靠性需求的大型存储。

* **RAID 10(RAID 1+RAID 0,镜像+条带化)**

* **特点**:结合RAID 1和RAID 0,先镜像再条带化,需至少四个磁盘。

* **优点**:高性能和高冗余,适合高负载环境。磁盘容量 N/2

* **缺点**:成本高,存储效率仅50%。

* **适用场景**:高性能、高可靠需求的场景,如数据库服务器。

* **RAID 50(5+0)**

* **特点**:结合RAID 5和RAID 0,多个RAID 5阵列组成条带化。

* **优点**:比RAID 5性能更高,允许单个RAID 5组内磁盘故障。

* **缺点**:需要更多磁盘,成本较高。

* **适用场景**:需要性能和冗余平衡的大型存储。

## 死锁

最少资源计算

`最少资源数\=进程数×(每个进程的最大资源需求−1)+1`

理解

- 为了 **避免死锁**,不单单是看资源数量,**还需要避免循环等待**,即通过合理的资源分配策略确保 **至少一个进程能够完成并释放资源**。这就涉及到一种更安全的策略:**保证系统能够安全地分配资源**,而不是简单地计算资源数量

因为要至少保证一个进程能获得他需要的资源,所在需要加这1个

- 目录

- Lua

- 常用接口

- 协同程序

- 文件IO

- 错误处理

- 面向对象

- Scheme / Racket

- 技巧

- 如何设计递归

- 导入自定义文件

- []与() 的区别

- 打印函数

- 函数实现设计诀窍

- trace 打印调试信息

- 命令

- racket 运行

- raco 打包

- 语法

- 向量 / 结构体 / cons / list / string?等检查类型

- 符号 / 字符 / 字符串

- if / and / cond 条件分支

- 类型判断 / 等式判断

- local 组织函数

- 测试函数

- Rust

- 命令

- rustup

- Cargo

- rustc

- Rustfmt

- C++

- 快速入门

- 技巧与概念

- pragma comment

- socket 编程

- 编译

- 引入库的 <> 与 "" 的区别

- 语法

- 基础类型

- 运算符表

- 运算符重载

- 命名空间

- const和mutable的使用

- c++1新特性

- nullptr / constexpr (c++ 1x)

- auto / decltype 类型推到 (c++ 1x)

- 循环数组 区间迭代

- if-switch-变量声明强化

- 面向对象

- 原始字符串字面量 R"

- 指针

- 内存泄漏

- 指针与引用的差别

- const修饰指针

- 智能指针

- 数组

- 对象

- 构造函数

- 虚继承/虚基类

- 虚函数和纯虚函数

- 抽象类

- 栈中实例化 / 堆实例化

- 实例类型转换

- 继承 公有 / 私有 / 保护

- 子类调用父类

- 多重继承

- 实例指针(this)

- 友元函数 访问类私有和保护的成员

- 构造函数、explicit、类合成

- 多态的应用

- new和delete的使用

- 函数

- 引用传值/指针传值

- inline函数

- Lambda 表达式

- 模版

- 函数模版

- 类模板

- 容器

- std::array

- std::vector

- std::ist / std::forward_list

- map 各种map

- 各种 set

- 元组

- 正则

- 并发

- thread

- 锁

- 异步访问

- 条件变量

- 原子操作

- 命令

- g++

- make

- vcpkg

- clang++

- pkg-config

- 常用实例

- fork 方式创建后台进程

- 第三方库

- folly 工具库

- QxOrm

- catch 测试框架

- MSYS2

- pacman

- c++ 性能追踪

- gperftools

- gprof

- Qt

- Qt 代码风格

- qt 项目框架

- Qt Design Studio

- 技巧

- 添加 .pri 项目

- 添加子项目

- 加载第三方库

- 中文不乱码

- 信号和槽

- 国际化

- 定制帮助系统

- 多媒体

- 数据验证器

- 伙伴快捷键

- 单词补全

- QPushButton 样式问题

- 为元素添加滚动条

- 指定图标

- 自定义的结构体支持串行化

- 界面数据存储与获取

- 匿名函数

- 预编译

- 升级浏览器内核

- 封装弹窗

- 命令

- qmake

- 命令行编译

- pro 文件

- CONFIG

- TEMPLATE

- windeployqt 打包

- jom

- 知识

- 元对象系统(MOC)

- 对象树与拥有权

- 各个 TextEdit 的区别

- Qt 资源系统

- QSS 查询

- QObject的创建时间

- qt 的继承关系

- 单元测试

- 宏

- 测试类/函数

- GUI测试

- Benchmark测试

- 实例

- 在子项目中创建

- 数据驱动测试程序'

- 模拟GUI事件

- API

- 控件

- QInputDialog

- QIcon

- QFileIconProvider 提供文件icon

- QActionGroup

- QSystemTrayIcon

- QMenu

- QWidget

- QLabel

- QTextBrowser

- QTextEdit

- QPushButton

- QRadioButton

- QDockWidget

- QMainWindow

- QKeySequence 预设快捷键

- QSplashScreen 启动图

- QListWidget

- QTreeWidget

- QTreeView

- QTreeWidgetItem

- QTreeWidgetItemIterator 遍历QTree

- QTableWidget

- QTableView 基类

- QTableWidgetItem

- 条目控件

- 条目的拖拽

- 自定义右键菜单

- 基于条目控件的样式表

- QWebEngineView

- 模型

- QFileSystemModel 文件系统

- QStandardItemModel

- QAbstractItemModel 基类

- QAbstractItemView / QStandardItem

- QSortFilterProxyModel

- 布局

- 布局分类

- QSplitter 分裂器

- QSizePolicy 伸展

- 伸展因子

- 伸展策略

- BoxLayout 布局

- FlowLayout 流式布局

- QGridLayout 栅格布局

- QFormLayout 表单布局

- 文件系统

- QFile

- QFileInfo

- QStorageInfo 分区信息

- QTemporaryDir

- QTemporaryFile

- QDir

- QFileSystemWatcher 监控文件

- QLockFile

- 字节与流

- QByteArray

- QDataStream

- QTextStream

- 进程

- QProcess

- 线程

- QMutex

- QReadWriteLock

- 并发方案

- 继承 QObject [推荐]

- 继承 QThread

- QRunnable与QThreadPool 配合

- QtConcurrent

- Application::postEvent

- 图像

- QPainter

- QPixmap / QBitmap

- QImage

- QPicture

- QImageWriter 创建图片

- QImageReader 读取图片信息

- 命令行工具

- QCommandLineParser

- 关联容器

- QStack

- QVector

- QLinkedList

- QQueue

- QList

- ====== 顺序容器 ======

- QMap

- QHash

- QMultiMap 一key 多value

- QMultiHash 一key多value

- QCache key映射到类

- QPair

- QSet

- ====== 关联容器 ======

- QVariant

- QVariantList

- QVariantMap

- QMetaObject 元对象,反射

- invokeMethod

- 实例

- 反射类名

- 反射实例

- 数据库

- mysql 链接

- sqlite 内存版

- QSqlDatabase 连数据库

- QSqlQuery

- QSqlTableModel 绑定表

- QSqlQueryModel

- 日志

- myMessageOutput 自定义日志格式

- 网络

- QLocalServer/QLocalSocket

- QTcpServer / QTcpSocket

- QNetworkAccessManager 异步API

- QSslSocket

- QUdpSocket

- QUrl

- QUrlQuery

- 系统

- QStandardPaths

- QDesktopServices 桌面服务

- QSysInfo

- 日期和时间

- QDate

- QDateTime

- QTime

- 异常处理

- QException

- 正则

- QRegExp

- 字符串

- QStringRef

- QUuid

- Core

- Q_PROPERTY 属性

- QGlobalStatic

- QSharedData

- QCoreApplication

- 全局 qxxx

- qSort / qStableSort 排序

- qRegisterMetaType 注册自定义类型

- qSetMessagePattern 改qDebug格式

- qInstallMessageHandler

- QCryptographicHash 加密

- QSettings

- QTimer

- QObject

- 设计模式

- 工厂类

- 单例模式

- 第三方库

- FluentUI UI框架

- Felgo 可做移动端

- Dart

- 语法

- 基础类型

- 运算符

- 函数

- 类

- 控制流程语句

- 异常

- 映射

- 异步支持

- Future / Stream

- async/await

- 容器

- Map

- List

- Set

- 库和可见性

- 测试

- pubspec.yaml

- Flutter

- 安装

- 插件

- 插件继承 implements

- 与原生通信

- 技巧

- 混合开发方案

- State Widget 生命周期

- 自动切换Andrio和Ios 主题

- 切换主页面缓存

- 跨平台 Plugin

- 同时调试flutter 和原生

- 命令

- flutter

- flutterfire 构建 Firebase

- fvm

- build_runner 代码生成

- melos 老dart 的 monorepo

- 常见组件

- 布局

- sliverList

- 响应式

- 交互

- cupertino IOS 风格

- 资源与图片

- Packages

- 路由

- Builder / FutureBuilder

- Stream

- theme

- RepaintBoundary 隔离重绘

- 三方库

- Getx 状态管理

- shared_preferences 存储

- webview_flutter

- FluroRouter 路由

- flutter_hooks 像 react hook

- hooks_riverpod 状态管理

- serverpod 服务端

- Pigeon 与平台原生通信

- amap 高德的地图

- flutter_launcher_icons 启动图标

- flutter_native_splash 启动页

- sqlite 数据库

- ====== UI库 ======

- macos_ui 实现mac ui

- fluent_ui winUI

- 实例

- 放大图片

- Python

- 技巧

- 语法

- 字符串

- 字典

- 装饰器

- 类

- 异常和错误

- 异步 python 3.x

- 场景

- 文件读取

- 内置包

- 包

- 工具类

- Supervisor-Linux/Unix进程管理工具

- 网络

- urllib包

- requests-比urllib2简洁

- BeautifulSoup-解析html

- 数据库/ORM

- pymysql -python3的mysql库

- SQLAlchemy ORM

- 办公

- pdfminer3k-解析pdf

- 测试 & 安全

- faker -测试

- web 框架

- web.py框架

- Django框架

- 模型

- gui

- easygui_gui模块

- tkinter - 高效简单

- pyqt5 - 控件丰富

- 单元测试

- doctest模块

- unittest模块

- 命令

- pip

- poetry 高级pip

- virtualenv 虚拟环境

- Java

- java 数组

- java 类

- java 包

- java 异常

- java String

- java 集合

- PHP

- 常用场景 / 封装

- appkey/secretKey 实例

- https双向认证

- 从字符串中找出高频词

- 操作 HTML DOM

- levenshtein 输出错误,猜测输入的值

- ip 查询

- 配置webhook.php

- php 输出图片

- ignore_user_abort 网页断开有效

- 原生支持异步的方法 exec

- 可自动结束的程序

- 循坏程序

- ===== 函数 / 类封装 ⬇ =======

- 指定月份的第某个月

- 时间类封装 某天的开始与结束

- 数据库链式调用封装

- curl 封装 / 发送文件 / 远程下载到服务器

- 下载进度条 / 断点续传

- 获取 win / linux 的mac地址

- exec 控制 cli 服务器的启动与停止 linux 版本

- 代码规范及技巧

- PHP的优化之道

- PHP 代码简洁之道

- PHP The Right Way

- PHP标准规范

- PSR-3 日志接口规范

- PSR-4 自动加载规范

- PSR-6 缓存接口规范

- PSR-7 HTTP 消息接口规范

- PSR-11 容器接口

- PSR-13 超媒体链接

- PSR-14 事件分发器

- PSR-15 HTTP 请求处理器

- PSR-16 缓存接口

- PSR-17 HTTP 工厂

- PSR-18 HTTP 客户端

- PHP注释规范

- php7+

- PHP WEB框架

- Slim 微型框架

- yaf

- RPC-yar

- 内置函数

- hyperf 高性能框架

- swoole

- 安装

- HttpServer

- WebSocket

- AsyncIO

- Swoole-Crontab

- 异步文件系统IO

- 异步Redis

- 异步MySQL客户端

- process

- Memory 内存操作

- Channel 连接池

- swoole与tp5

- 调试 swoole

- 示例

- websocket 绑定对象方法

- redis 事件订阅发布

- EasySwoole

- 技巧

- 对自定义类优化的方式

- 数据库

- 基础使用

- 定时器

- 自定义命令

- 自定义进程

- 自定义事件

- 异步任务

- Crontab 定时任务

- 日志

- 组件库

- 单例模式

- Di 容器 / 依赖注入

- 协程 / WaitGroup

- 内存 Table

- Csp 并发等待执行

- 队列 Queue

- SplArray

- SplBean 过滤表结构

- 缓存

- 热重启

- 控制器

- TP5

- 验证器

- 内置规则

- 数据库操作

- 数据添加或更新

- 静态增删改查 / 关联操作

- 日志操作

- 路由

- taglib-自制标签

- migrations 数据库迁移

- tp 测试

- TP3.2

- 数据库操作

- 关联表

- 增删改查与验证

- 前置与后置

- 发送邮箱

- Tp6

- 技巧

- 多应用的api版本控制

- phinx 迁移工具

- 单元测试

- 先使用修改器在验证

- 异常统一处理

- thinkcmf

- 快速入门

- 常用插件

- 小程序管理插件

- 手机微信登录插件

- 表单自动生成插件

- phalcon C框架

- 快速入门

- 脚手架教程

- Symfony

- Swoft

- laravel

- webman

- workerman

- Spiral Framework

- composer / C扩展

- 网络 / curl / 文件上传 / jwt 认证

- guzzle [19.8k] http 客户端

- php-curl-class[2.6k] 封装curl为类

- class.upload.php 文件上传

- codeguy/upload 文件上传

- php-jwt 封装 JWT 加解密

- 文本 uuid / 加密整数id / 中文转拼音 / 解析html

- uuid 生成uuid

- hashids 隐藏真实id

- pinyin 中文转拼音

- html-parser 类jquery解析 html

- i18n

- i18n 国际化

- gettext 国际化

- 数据验证 / mock数据 / 媒体类型

- faker 生成验证数据

- Analyzer 检验媒体资源类型

- Valitron [1.3k] 数据验证

- rakit/validation [399 star] 验证数据

- 支付

- OmniPay 多网关支付处理的框架

- 时间

- Carbon [14.6K]

- 日志 monolog / seasLog

- monolog php编写

- SeasLog C扩展

- 办公文件 pdf / word / excel / ppt

- Snappy 一个PDF和图像的生成库

- WKHTMLToPDF HTML转换为PDF

- PHPPdf XML转化为PDF和图片

- PHPWord - 处理Word文档

- PHPExcel 处理Excel文档

- PHPPowerPoint -处理PPT幻灯片

- 性能分析 xhprof

- xhprof - PHP性能追踪及分析工具

- 缓存 yac

- Yac 5.2+ 共享缓存

- 配置 yarconf / 解析 json xml ini yaml

- yarconf 7.0+ 读取配置

- config 解析 json xml ini yaml

- 队列 resque (基于redis) / beanstalkd

- Beanstalkd 队列

- php-resque 基于redis的消息队列

- web ui 管理 / redis / pgsql / mysql / mgdb

- phpRedisAdmin - Redis 管理

- phpPgAdmin - PostgreSQL管理工具

- phpMyAdmin - MySQL管理工具

- rockmongo - MongoDB管理工具

- ORM

- medoo 支持5大数据库

- Redis C 扩展

- mongodb C扩展

- mongo-php-library 官方基于C扩展到的封装

- MongoDB ORM

- ElasticSearch PHP 用于 ElasticSearch 的官方客户端库.

- 调试与性能

- nette/tracy 优化报错

- 状态机

- Finite 有限状态机

- 定时任务

- jobby

- 邮箱

- php-imap 接收邮箱

- PHPMailer 发送邮箱

- Sphinx - 全文索引

- JsonMapper 一个将内嵌JSON结构映射到PHP类上的库

- weichat 封装

- User Agent 检测

- class.upload.php 文件上传

- 官方库

- SPL 数据结构

- SplDoublyLinkedList 链表

- SplStack 栈

- SplQueue 队列

- SplHeap 堆

- SplMaxHeap / SplMInHeap 大排序

- SplObjectStorage 存储对象列表

- SplFixedArray 固定长度的数组

- 预定义接口

- Iterator while迭代

- ArrayAccess 数组式接口

- Serializable 序列化接口

- IteratorAggregate foreach迭代器

- Observer 观察者

- SPL 函数

- spl_autoload_register 自动导入类

- class_parents 返回指定类的父类

- spl_object_hash/spl_object_id

- SPL 常见异常

- SPL 迭代器

- DirectoryIterator 文件目录迭代器

- FilesystemIterator 文件迭代器

- GlobIterator 带匹配的文件系统

- ArrayIterator 把数组改成迭代器

- NoRewindIterator 只遍历一次

- RecursiveArrayIterator 递归迭代

- RecursiveTreeIterator 输出递归树

- SPL 文件处理

- SplFileInfo 文件信息

- SplFileObject 文件操作提供对象

- SplTempFileObject 临时文件

- Ctype 类型检测

- ctype_alnum 是否只有字母和数字

- ctype_alpha 是否是字母

- ctype_cntrl 是否是控制符(\n\t\r)

- ctype_digit 是否是整数

- ctype_lower / ctype_upper 是否是 小/大 写字母

- ctype_graph 是否是可见字符(空格不算可见)

- ctype_print 是否是可见字符(空格算可见)

- ctype_punct 是否是除字母,数字,空格外的特殊字符

- ctype_space 是否是空白字符

- ctype_xdigit 是否包含16进制字符([0-9 和 [A-Fa-f] ])

- 数组

- array_map-针对多个数组

- array_multisort 对二维数组进行排序

- array_filter

- array_walk - 对一个数组操作

- array_walk_recursive 递归

- filter 过滤器函数

- 预定义常量

- filter_has_var 存在指定变量

- filter_var 过滤变量

- filter_var_array

- filter_input_array 过滤外部变量

- filter_input

- 控制输出 flush

- flush 刷新输出缓冲

- 实战

- 安全转义参数

- htmlspecialchars html标签转实体

- addslashes 用反斜线转义(可用于数据库)

- quotemeta 转义特殊字符

- 日期/时间/日历

- format 参数列表 如 Y,m,d

- DateTime 时间函数

- cal_days_in_month 某个月的天数

- date_parse_from_format [函数] 根据日期格式转时间

- 异常处理

- set_error_handler

- set_exception_handler 自定义异常

- URL 处理函数

- get_headers 获取头信息

- http_build_query 数组转 query

- parse_url 解析 URL 返回数组

- urldecode 和 urlencode

- 字符串处理

- strstr 字符串的首次出现

- chunk_split 将字符串分割成小块

- chr / ord 字符与ascii转换

- str_split 将字符串转换为数组

- htmlentities / htmlspecialchars 等 html 编解码

- strip_tags 字符串中去除 HTML 和 PHP 标记

- uniqid 返回唯一值

- preg 函数

- preg_grep 从数组返回匹配的值

- preg_last_error 正则匹配错误

- preg_match / preg_match_all

- preg_replace 正则替换

- preg_replace_callback

- preg_split

- 进制转换

- bin2hex / hex2bin 字符串-16进制

- bindec / decbin 十进制-二进制

- octdec / decoct 八进制-十进制

- base_convert 任意进制转换

- 文件系统函数

- fopen / feof / fclose 适合文件和网页

- fread 按字节读取

- fgets 按行读取

- fwrite 写入文件

- file 一次读取整个内容,行遍历

- fscanf() 每行都根据格式循环输出

- file_get_contents 一次读取所有,返回完整字符串

- flock 文件锁

- disk_total_space 磁盘容量

- 文件 / 路径处理

- scandir 返回指定路径的目录和文件

- glob 使用 * 模糊搜索文件和目录

- is_dir / is_file

- opendir / readdir / closedir 循环输出文件/目录名

- dirname /basename 父路径 / 基础文件

- pathinfo 文件路径的信息

- realpath 真实路径

- copy / rename 复制 / 重命名

- touch / unlink 创建/删除

- file_exists 文件是否存在

- filesize 获取文件大小

- is_readable / is_writable / is_executable

- 文件权限

- fileperms 获取文件权限

- 反射

- ReflectionClass 反射类

- ReflectionExtension 反射扩展

- ReflectionFunctionAbstract

- ReflectionFunction 反射函数

- ReflectionParameter 函数,类的参数

- ReflectionProperty 类属性

- ReflectionType 参数或返回值的类型

- 协议

- php://

- input / output

- stdin / stdout / stderr

- memory / temp

- filter

- ftp:// 和 ftps://

- data://

- glob:// 文件路径模式

- 过滤器

- 字符串过滤器

- 转换过滤器

- stream

- Stream Filters

- Contexts

- socket

- PDO

- PDO::setAttribute 属性

- 加密扩展

- password_hash

- openssl

- 杂项函数

- sys_getloadavg 获取系统的负载

- hrtime 微妙时间戳

- ignore_user_abort

- uniqid

- sleep/usleep

- imap 邮箱

- Session

- Callback 类型

- exec 执行结果以数组返回

- socket_create 操作

- soap 调用 webserver

- C / C++框架 编写扩展

- 原生编译

- 引用 加载动态库(.so) 文件

- 参数、数组和Zvals

- Zephir 开发PHP扩展

- 安装

- 快速入门

- php-cpp C++开发扩展

- 安裝

- 技巧

- 语法

- 变量

- 常数

- 输出和错误

- 函数

- 指定参数

- 调用PHP函数

- Lambda函数

- 构造函数

- 魔术方法

- 基础SPL接口

- 扩展类的魔术方法

- 类属性

- 异常

- 读取php.ini变量

- 扩展回调

- 命名空间

- FFI PHP扩展方式

- pear / pecl

- pecl c 扩展

- 在多 php 版本中指定

- pear php 扩展

- 安装/编译

- oneinstack 一键配置

- lnmp /lamp 脚本安装

- 配置 Let's Encrypt

- 配置 thinkphp

- dnmp docker 安装 LNMP

- ==== php 环境一键安装 ====

- Centos

- Ubuntu

- macOS

- ==== 包安装 ====

- apache

- nginx

- php

- 安装 GD 扩展

- 安装 openssl 模块

- ==== 编译环境安装 ====

- window apache/php

- window nginx/php

- PHPUnit

- 编程写测试

- 添加测试的依赖

- 数据供给器

- 对异常进行测试

- 对输出进行测试

- 基境 测试初始化与还原

- 数据库测试

- php 扩展

- opcache 缓存编译

- 常用正则

- php.ini 最佳实践

- php 调用 jar包

- Golang

- 知识碎片

- 无锁编程

- 调度器

- 预防CSRF攻击

- 避免XSS攻击

- 避免SQL注入

- 存储密码

- 设计模式 / 规范 / 性能 / 技巧

- 设计模式

- 单例模式-数据库单例

- 值选项模式

- 组合模式

- 策略模式

- 规范

- 性能优化

- 技巧

- 高性能

- 字符串拼接性能

- 切片性能及陷阱

- for 和 range 的性能比较

- Reflect 提高反射性能

- 逃逸分析

- 死码消除与调试(debug)模式

- sync.Mpap 与 加锁map

- 项目布局

- 项目布局一

- 项目布局二

- DDD分层架构

- 数据类型

- 切片类型( slice)

- 场景

- 请求/响应/错误码设计

- gin 对 handle的封装

- 带超时的 sync.WaitGroup

- 优雅关闭协程

- 控制协程的并发数量

- 并发非阻塞缓存

- 守护其他进程的代码

- 各类型转 sturct

- 注册为window 的服务

- go 注册

- sc 注册

- nssm 注册

- udp 打洞

- udp 打洞转 tcp

- Reader 用法

- i18n 本土化

- 压缩编译体积

- 第三方库

- 操作 DOM

- goJquery 像 jQuery一样操作DOM

- ORM

- gorose -链式调用

- GORM

- 技巧

- 获取一对多

- dbx 支持缓存全表数据

- sqlx

- 路由 / http客户端 / websocket

- httprouter 实现RESTful 风格

- mux - 路由

- fasthttp 比 net/http 快10倍

- GoRequest http 客户端

- gorilla库 路由 /参数转结构体

- gorilla/mux URL路由和分发器

- gorilla/schema 参数转换为结构

- websocket

- balloons-websocket 封装好的 websocket

- melody 优雅的websocket

- nhooyr-websocket 性能好于gorilla

- gorilla/websocket [14.5K]

- 缓存 / 并发

- go-redis

- gocache 封装 redis,memcached,内存的缓存

- cache2go 带过期回调的缓存

- go-cahce 类memcached 可存文件断电恢复

- tiedot 内存NoSQL数据库

- Gcache 带过期,带操作事件,支持 LFU,LRU ,ARC

- concurrent-map 支持并发的map

- bigcache 分片map缓存,value 只能存byte

- golang-set set的go实现

- atomic 支持更多类型

- conc 更好的结构化并发

- map转struct / 打印结构体

- mapstructure map 转 struct

- litter 优雅打印结构体

- 数据结构

- 结构算法库 Lists / Sets / Stacks / Maps / Trees

- 工具库

- pie 常用数组操作

- lo 类似 Lodash

- 连接池

- go-common-pool

- ants

- 序列化库 json / ini / yaml

- jsoniter 官方更高效的 json 库

- easyjson免运行时反射的json化

- gjson 从json中取值或判断

- simplejson 处理未知结构的json

- props 解析各种 ini / yaml 等

- 支持Unmarshal map 转配置

- viper 11k Star 支持yaml,ini 支持 env ,命令行 等

- hash / uuid

- xxhash 返回整数类型

- uuid

- Log 日志库

- zap 高性能日志

- Logrus 可插拔日志

- GUI

- fyne 简单难看的 GUI

- go-qt

- wails 桌面gui go + vue

- webview 用 html 可直接编译跨平台 app

- vugu vue+WebAssembly

- termui [11.6k]

- 命令行 / TUI

- urfave/cli [14.3k] 命令行

- kingpin 简单强大命令行

- cobra [18.2k] 专业级命令工具

- x-mod/cmd 空格隔离参数

- mpb 进度条

- progressbar 另一个进度条

- rivo/tview [4.5k] 命令行ui

- cute 漂亮的输出

- bubbletea 强大的 TUI

- 检验 validator

- validator

- 定时器

- cron 简单,不可修改的定时器

- cronlib 可修改任务 推荐

- robfig/cron 支持cron 和 固定时间

- 加密库

- thinkoner/openssl 可支持 ECB、CBC等

- 自己封装的加密库

- 身份验证和OAuth

- authboss 认证

- go-oauth2-server 符合规范的OAuth2服务器

- 开源 IM

- tonyboxes/imgo

- GoBelieveIO/im_service

- alberliu/gim [1.2k]

- 流量控制 / 熔断器 / 容错

- hystrix-go

- 示例

- Hello World

- http 示例

- dashboard 可视化

- Sentinel GO 流量控制组件

- QPS

- 热点参数限流

- 熔断降级

- 静态资源打包

- go-bindata 静态资源打包进执行文件

- 爬虫/无头浏览器

- colly [11.9k]

- chromedp 可控制是否显示浏览器[9.6k]

- 实例

- 启动访问某个网站

- 访问网站并且截图

- 设置cookie,保持登录状态

- 下载文件

- emulate 设备模拟

- 代理

- goproxy 代理

- 聊天机器人

- chatbot

- 图像

- imaging 图像处理

- gg 图像处理

- 单元测试

- gomonkey 打桩函数 - 推荐

- goconvey 测试结果带UI

- sqlMock

- redisMock

- httpmock

- Testify 支持断言,写法更简便

- gocheck 测试框架

- faker 生成假数据

- 依赖注入

- fx User开发的依赖注入

- 注册一个http

- 添加 handle

- 添加日志

- 注入接口

- 注入多个接口

- MIME 文件检测

- mimetype 类型检测 [1.2k]

- filetype [1.9k]

- 全文索引

- bleve

- fsnotify 文件监听

- gopay 支付集合

- .env 环境变量

- 哈希算法 转整数

- gopsutil 系统性能数据

- 官方包

- C

- 简单调用 c函数

- c与go 类型转换

- go 类型转C类型

- panic / recover

- panic+recover简化错误处理 模块必学

- error 自定义错误结构体

- unsafe

- archive

- tar

- zip

- bufio

- bytes

- compress 压缩

- gzip

- zlib

- container 数据结构

- heap

- list

- ring

- index/suffixarray 字典树

- Context

- crypto 加密

- rsa

- md5

- sha1

- sha256

- sha512

- tls

- database

- sql

- encoding

- encoding

- base32

- base64

- binary 序列化

- csv

- gob

- hex

- json

- xml

- errors

- expvar - 线性安全全局变量

- flag

- fmt

- 格式化输出格式

- html

- html

- template

- image

- image

- color

- png

- draw 图像合成函数

- gif

- jpeg

- io

- io

- ioutil

- log

- syslog

- math

- math

- rand

- net

- net

- http

- cookiejar 自动存储cookie

- httptest http的mock

- httptrace 追踪http

- httptest

- httputil 反向代理,打印头信息

- pprof

- rpc

- smtp

- url

- textproto

- os

- os

- exec

- signal

- user

- path

- path

- filepath

- plugin

- reflect

- regexp 正则

- runtime

- runtime

- debug

- pprof

- trace

- sort

- strconv

- strings

- sync

- atomic

- testing

- doc

- testing

- quick

- text

- scanner

- template

- time

- unicode / utf8

- unicode

- utf8

- utf16

- embed 嵌入

- js WebAssembly

- 示例

- golang.org/x

- net

- ctxhttp 带 ctx 的请求

- nettest

- netutil

- websocket

- oauth2

- crypto

- ssh

- text

- xorm / xorm+odbc

- go 适配 odbc

- 其他技巧

- 查询条件方法

- 关联查询

- 缓存

- 增删改查前后置的操作

- 同时支持三个数据库需求

- cmd 自动生成结构

- 嵌入 logrus

- web框架 / 微服务框架

- gin 框架

- 语法

- 中间件

- 参数模型绑定

- hmtl 渲染

- JSONP

- BasicAuth 基础认证

- 路由

- 输出格式

- 重定向

- 异步处理

- 静态资源

- 实例

- HelloWorld

- go-gin-example

- gin-vue-admin

- 测试

- beego

- 模型操作

- generate 生成的模型操作

- 一对一查询

- 一对多

- 打印日志

- 路由

- iris web 框架

- kratos bilibili 开源

- gf web/tcp 4.3K集大成框架

- gf-cli 命令行工具

- tcp 组件

- endless 热更新

- echo

- ====== web 库 ======

- Goji微框架

- go-zero [5.2k] web / 微服务框架

- go-micro 14.9K 微服务框架

- 快速开始

- 技巧

- 命令

- micro

- dashboard

- 示例

- HelloWorld

- 用户模块示例

- Jupiter 2.5K 微服务框架

- ====== 微服务 ======

- go-admin

- Gin-Vue-Admin

- gfast

- Simple Admin

- ====== Admin 后台 ======

- RPC / ARPC

- net/rpc

- net/rpc/jsonrpc 不支持http

- RPCX 分布式的RPC

- 元数据 / 分组

- 心跳

- 单服务例子

- 多服务例子

- 异步回调例子

- Fork 发送多个rpc有个成功

- broadcast 广播模式

- UI管理工具

- erpc

- arpc

- tcp / tcp 框架

- 最简单的 tcp 连接

- 面向对象,带有类型的tcp连接

- tcp binary 设置协议头

- 完善的tcp 服务端/客户端管理

- tcp server 框架

- zero - [152]

- xtcp - [101]

- gotcp - [458]

- Zinx - [3K]

- Go Web 编程

- go web

- websocket

- go cli

- godoc

- 约定

- Example

- go build

- buildmode 编译不同结果

- 编译 *.so 的动态链接

- pgp 示例

- 条件编译

- +build 条件编译

- go:build 推荐

- 文件后缀编译

- go:build 条件编译

- mod

- gcflags 逃逸分析等

- asmflags

- -ldflags 编译优化等

- go run

- go install

- go get

- go generate

- go test

- -bench 压测

- http 测试

- fuzz 模糊测试

- go mod

- go tool trace 性能追踪

- go tool pprof 性能追踪[推荐]

- 封装 pprof 可指定端口

- statsviz 运行时统计信息

- go tool dist

- work

- 编译工具

- xgo 一键编译多平台

- goreleaser 快速上传各架构编译到github

- go 国产化编译

- air 监听go,实时编译

- golines 自动换行

- go 支持 oracle

- go 调用dll

- dlv 远程调试

- 服务器

- Git

- 知识

- codeowners 指定目录所属

- 命令

- config

- commit

- rebase

- merge 分支合并

- cherry-pick

- checkout 切换/创建分支

- branch 创建/删除分支

- clone

- diff

- reset

- revert 取消某个提交

- rm / mv

- mergetool 可视化合并冲突

- log / reflog

- stash 搁置

- tag

- show

- pull / fetch

- push

- remote

- submodule 子模块

- shortlog log日志汇总

- archive 打包

- sparse-checkout

- git lfs 管理大文件

- rev-list

- filter-branch 历史中删除不该提交的文件

- bisect 二分查找

- format-patch 导出补丁

- worktree 便捷clone

- 技巧

- HEAD^ / HEAD~ 差别

- git 使用 rsa

- window 重新设置账户密码

- commit 规范

- 生成 Change log

- 规范流程

- commit 图标

- 分支命名

- centos git 服务器

- Nginx

- 技巧

- location 匹配

- 场景

- http 代理 / 超时设置

- 静态站点 / 动静分离

- 负载均衡

- 限流配置

- HTTP/2 服务推送

- 匹配路径跳转

- 缩略图

- 优化

- reuseport 负载均衡 [nginx>1.9]

- linux 内核参数优化

- nginx.conf 配置

- open_file_cache

- 自定义 access.log 格式

- Apache

- 常见场景

- .htaccess 场景

- 切割日志

- 改写重定向权限

- rewrite日志功能

- ip限制

- 目录列表功能

- 响应头的 Server 信息

- 代理 / 重定向

- 配置 https

- 添加响应头信息

- 限制目录访问

- 某目录不解析 php

- 允许跨域

- mpm 三种并行处理模块

- Caddy 类Nginx

- Caddyfile

- Caddyfile 指令

- root

- header

- php_fastcgi

- rewrite / try_files / uri 代理

- redir 重定向

- encode 压缩

- basicauth http认证

- handle / handle_path 类似nginx 的location

- reverse_proxy

- metrics 统计

- 场景

- 设置静态文件

- 自动跳websocket

- 真实域名设置https

- 代理

- php 服务

- 命令

- 监控日志

- OpenResty 带lua 的nginx

- ====== 常用工具 ======

- protobuf 协议

- 安装

- protobuf

- gogo

- protoc 命令

- 语法

- proto3的变化

- 示例

- golang 实现

- grpc

- golang 实现

- ====== 传输协议 ======

- opentracing 标准

- jaeger UI 优化,更简单

- 实例

- 带 context 的追踪

- 以 span 追踪

- http 形式访问

- 使用Inject和在进程之间

- rpcx 调用 [通过 conetxt ]

- rpcx 调用[通过传递 string(tranid,spanid,parentSpanId)]

- Zipkin

- ====== 链路追踪 ======

- jenkins 持续集成/交付

- 推荐设置

- 技巧

- webhook -通过gitlab 触发

- 远程触发编译

- 添加节点

- 构建一个go

- 常用环境变量

- 构建方式

- pipeline

- 设置环境变量

- 实例:Jenkinsfile

- 示例:使用多个agent

- 参数化构建

- MultiJob Project (新版弃用)

- 插件

- Go Plugin 插件

- git 无变化跳过构建

- Folders Plugin 创建任务分组,方便管理

- Multiple SCMs Plugin [新版本弃用]

- 生成时间戳

- FTP 传送到应用服务器

- Publish Over SSH 发送到远程

- 角色及权限管理

- 备份

- pipeline

- blue ocean 可视化 pipeline

- junit 测试报告

- Cobertura Plugin 可视化覆盖率

- cds 持续集成

- Travis CI 教程

- GitLab

- 持续集成 CI/CD

- 安装Runner环境

- .gitlab-ci.yml 配置

- CI/CD Examples

- 备份还原

- Gitea git 自托管

- ====== 持续集成 ======

- Zabbix 服务器监控

- prometheus 时序处理,报警系统

- 概念

- 工作流程(推荐阅读)

- 数据类型

- 作业和实例

- 联合

- 命名

- 安装

- 组件

- prometheus.yml 配置

- 数据模型

- PromQL

- 运算符

- 函数

- 查询

- HTTP API

- 记录规则

- 警报规则

- 配置

- 告警规则

- 示例模板

- Alertmanager

- 配置 Alertmanager

- 实例

- 监控程序启动

- 监控cpu,内存告警

- 服务发现

- 基于文件的服务发现

- 实例

- 导入 prometheus

- 配置三个 node

- go demo

- grafana 图形分析器

- Grafana 变量

- 报警

- 配置邮箱接收

- 配置 webhook

- 通知策略

- 实例

- 开源监控方案

- go+influxdb+grafana 制作日志监控系统

- 数据库中获取数据展示

- goaccess 日志分析工具

- countly-server 网站统计

- go-netflow 监控程序流量

- tproxy 监测 grpc 与mysql 连接

- Monyog 监控mysql

- uptime-kuma 多功能监控

- SamWaf 网站防火墙

- kyanos 带ui 的tcpdump

- ====== 监控 ======

- metersphere 测试/压测/报告

- ====== 测试 ======

- beats 轻量型日志采集器

- Flume 分布式日志

- fluentd 日志处理

- 安装

- 配置文件

- 语法

- 公共参数

- 插件

- 输入插件

- tail 监听文件

- forward 接受到其他fluent

- tcp

- http

- exec 接受程序输出

- monitor_agent 监视器

- 输出插件

- file

- forward 转发到其他fluent

- http

- copy

- roundrobin 轮询输出

- stdout

- elasticsearch

- mongo

- mongo_replset

- 容器开发

- 实例

- HelloWorld

- PHP应用

- apache日志输出到mongod

- Addax 异构数据同步

- 示例

- Hello World

- Elasticsearch

- Loki grafana 的日志收集

- ====== 日志/数据 处理 ======

- Bazel 构建

- Make

- 技巧

- ====== 构建工具 ======

- HAProxy

- 安装与示例

- 配置详解

- 示例

- 搭建L7负载均衡器

- 搭建L4负载均衡器

- 使用Keepalived实现高可用

- Keepalived 虚拟ip

- ====== 负债均衡 ======

- pyroscope-server pprof 定位性能问题

- 示例

- go 示例

- ====== 持续profiling服务 ======

- proxmox 虚拟机管理

- Vagrant

- opentofu 云化管理,可回滚docker等

- Docker

- 规范的docker部署案例

- 场景

- phpstorm调用docker

- Docker 命令

- docker push / pull

- docker search

- docker images

- docker rmi

- docker commit 定制镜像

- docker tag 镜像标签

- docker save 导出镜像

- docker history 镜像创建历史

- docker buildx 构建多种系统架构

- ====== 镜像 ======

- docker run

- docker update 更新run的设置

- docker stop / start / restart

- docker pause / unpause 暂停/启动

- docker kill 杀到运行的容器

- docker rm

- docker attach / exec 进入容器

- docker export / import 导入导出

- docker ps 列出容器

- docker port 映射的端口

- docker top 类似top

- docker logs 容器日志

- docker inspect 容器元数据

- docker stats 资源情况

- docker cp 复制目录到容器

- docker diff 容器结构变动

- docker rename 重命名

- ====== 容器管理 ======

- docker login

- docker logout

- ====== Docker Hub ======

- docker swarm 管理集群服务

- docker-machine 模拟安装与使用

- vm 安装和使用

- docker service

- docker node 管理集群节点

- docker stack 文件方式编排

- 示例:部署WordPress

- ====== 集群管理(Swarm) ======

- docker network

- network create

- network connect

- network disconnect

- network inspect 显示细节

- network ls

- network prune 删除所有未使用网络

- network rm

- docker volume

- volume create

- volume inspect 详细信息

- volume ls

- volume prune 修剪

- volume rm

- docker system 系统管理

- system df 磁盘总体情况

- system prune 移除不用资源

- system info 等于 docker info

- system events 等于 docker events

- docker info docker 信息

- Docker-compose

- 命令

- docker 命令转 docker-compose

- Docker-machine 编排

- dokcer-machine create

- 安装

- Dockerfile 文件

- ENTRYPOINT 入口点

- docker-compose.yml

- 指令

- 私有仓库

- docker-registry

- Harbor

- UI界面

- lazydocker docker 命令行ui

- WeaveScope docker网页可视化

- lazykube k8s 界面

- Portainer 单机,集群可视化管理

- Rancher 企业级容器编排

- 实例

- redis 单机

- redis 集群

- docker-compose 搭建 lamp 应用

- php实战项目

- K8S

- 安装

- 容器可ping 外网 / 给容器局域网 ip

- 远程使用docker

- 缩小容器体积

- ====== 虚拟化 ======

- ffmpeg 音视频处理

- 实例

- 查看文件信息

- 转换编码格式

- 调整码率

- 改变分辨率

- 提取音频

- 截图

- 裁剪

- 为音频添加封面

- SRS 流媒体服务器

- ====== 流媒体 ======

- Casbin web访问权限控制

- Model 与常用配置文件

- 示例

- Hello World

- Http 示例

- gin 示例

- Casdoor 集成登录

- ====== web 组件 ======

- semgrep 静态代码扫描工具

- shellcheck 脚本lints

- ====== Lint ======

- Apollo 强大但部署麻烦

- Nacos 简单方便

- ====== 配置中心 ======

- 宝塔 面板安装

- 1Panel 运维管理

- 雷池 站点防护

- ====== Linux 面板 ======

- libreoffice 操作/预览office

- soffice 命令

- linux 中文字体问题

- 示例

- 预览 office(word,ppt,xsl) / pdf

- tika 文档转文字

- tika-server

- tika-app

- 示例

- http 请求获取文本内容

- go 与jar 配合

- ====== 文档 ======

- 禅道

- 快速入门

- ====== 项目管理软件 ======

- buildroot 交叉编译

- CGO 交叉编译实例

- onlyoffice 在线office编辑

- 安装

- 编译

- ubuntu16.04 编译

- 在uos_arm编译[弃]

- 修改字体

- 示例

- Hello-World

- ebpf 性能追踪

- Nexus Repository 统一包管理器

- go

- webdav

- chsrc 镜像自动设置

- certbot 自动配置https 证书

- Supabase 开源代替Firebase

- ====== 视频会议 ======

- jitsi-meet 视频会议

- 前端

- HTML

- 设计规范

- Web前端兼容性问题

- 手机端

- 尺寸单位

- rem 方案的示例

- JS / jQuery 插件

- 轮播图 滑动鼠标

- slick 鼠标滑动事件

- swiper 鼠标滑动 案例丰富

- 时间

- Moment 时间解析模块

- jQuery jquery-date-range-picker 日期区间

- jQuery daterangepicker 日期区间(美观)

- jquery bootstrap-datetimepicker 日期和时间

- 图片

- viewerjs 图片预览 功能全无需jquery

- grade.js 根据图片生成背景色

- js-cloudimage-360-view 360度旋转观看图片的 JS 库

- pagemap 网页右上角缩略图

- JQuery jqzoom.js-类似淘宝的图片放大

- jQuery lightBox-图片顺序预览

- JQuery Jcrop 图像裁剪

- X6 图形绘制工具

- 图形渲染

- D3

- SnapSVG svg 绘制库

- pixijs 绘制 WebGL,Canvas

- gojs

- three.js 做3D VR

- css3d-engine 精简版 treejs

- pano2vr 方便快速的3D-VR

- echarts

- 示例

- 动态时序图

- smoothie.js 监控图

- 工具库

- 下划线库 -有两个库

- licia 常用开发库

- Ramda 函数式库

- API

- 比较运算

- 数学运算

- 逻辑运算

- 字符串

- 函数

- 数组

- 对象

- MOCK

- json-server 伪造 json 接口

- mock.js 随机数据

- 文件上传 / 下载

- [推荐]filepond 文件上传 9.6K start 可编辑图片

- downloadjs 可让ie 支持文件下载重命名

- jQuery 多文件上传进度条 Huploadify

- 单元测试

- mocha 20K

- jest 33.2K

- 匹配器

- cypress 测试

- 视频播放

- flv.js b站开源

- jessibuca 支持webrtc

- media-chrome 视频播放器

- 大屏

- 拖拽式 大屏框架

- DataV 基于vue2 大屏

- 加密库

- CryptoJS

- 网页编辑器

- monaco-editor 网页版编辑器

- codemirror

- 移动端相关库

- better-scroll 更好的滚动

- Pxmu.js 通知,loading 等 [11 star]

- postcss-pxtorem 自动px 转 rem

- jQuery

- jQuery springy 关系可视化

- jQuery zTree 树插件

- jQuery select标签中搜索option

- jQuery jQueryUI

- 拖拽和放置

- 缩放

- 特效

- 滑动选择

- 排序

- 折叠面板

- 进度条

- 标签页

- autocomplete 自动完成

- jQuery form 表单提交插件

- jQuery Validate 验证

- 使用方式

- 校验规则

- 实例 validate与 jquery form

- jQuery Cookie

- jQuery Boostrap autocomplete

- jQuery Growl 侧边消息提醒

- jQuery noty 通知

- jQuery Migrate

- Slidev makedown 生成 PPT

- 语法

- makeDown

- Layouts

- theme

- 基础属性

- PlantUML

- components

- ORM

- typeorm

- 实体

- 一对一等处理

- 查找

- 生成器

- 验证

- 对象数据库

- sql.js 网页sqlite 数据库

- 示例

- node 使用

- web 使用

- 获取远程库

- pglite 网页版 pgsql

- prismjs 语法高亮

- introjs 新手引导

- RequireJS 客户端模块管理

- cleave.js 格式化输入框内容

- fusejs 搜索功能

- tesseract.js 文字识别

- fullPage 全屏滚动网站

- mjml 转为相应式邮箱html

- progressJs 头部进度条

- instant.page 链接预加载

- pdf.js

- Yjs 协议编辑

- 前端框架

- layui

- 常用方法

- layui.laytpl 前端模板

- 模块定义

- 常用库

- form_table

- Cron表达式组件

- notify

- layui-soul-table

- xm-select

- tableTree

- croppers 截图上传

- 技巧

- 打开表单

- 表单格式

- layuiAdmin 官方

- LuLu 灵活前端

- ====== 桌面框架 ======

- Frozen UI

- WeChat UI

- MUI 对移动端做了优化

- AUI js 框架

- ====== 移动端 ======

- ficusjs 使用 Web component

- ====== 原生 component ======

- htmlx 无js 页面交互

- CSS

- 知识

- 最佳网页宽度

- 产生空白间隙的原因

- 所有元素平滑动画

- 技巧

- 居中 / 对齐

- 顶端观看显示进度条

- 图片自适应同步的截取

- 元素硬件加速

- 滚动条样式

- 给列表加竖线

- 文字超出隐藏并显示省略号

- 打字效果

- 语法

- translate 移动

- transform 转换

- transition 过渡

- animation 动画

- ====== 动效 ======

- flex

- grid

- ====== 布局 ======

- 函数

- CSS 变量

- vw,ch 等长度

- box-sizing 属性

- ====== 技巧 ======

- Font Awesome 字体

- bootstrap v3

- 样式快速入门

- 基础样式

- 布局

- 文本

- 列表

- 表格

- 表单

- 按钮

- 图片

- 辅助类

- 关闭按钮

- 三角符号

- JavaScript 插件

- 模态框

- 标签页

- tooltip 提示

- 按钮 设置加载

- normalize.css 初始化

- animate.css 动效

- tailwindcss css类样式

- 安装

- 定制

- 配置 文件

- 组件

- 语法

- container 容器

- Box Sizing

- Display

- 浮动 / 清除浮动

- Object 可控替换元素

- overflow 溢出

- Overscroll 滚动区域边界时的行为

- position

- Top / Right / Bottom / Left

- visibility 可见性

- Z-Index

- Flex

- Justify Content 控制flex/grid的主轴

- Align Content

- Align Items

- Grid 网格布局

- Justify Items

- 间距

- 内边距 / 外边距

- space 控制子元素之间的间隔

- UnoCSS 类似 TailwindCSS

- water.css [7k] 无需class的框架

- simple.css [2.5k] 无需class的框架

- open-props css变量框架

- ====== css 框架 ======

- Sass/Scss与Less区别

- less 不依赖ruby

- z.less 库- 预定义常用函数

- stylus

- Sass 靠缩进继承

- scss = Sass 3 靠括号继承

- ====== css 库 ======

- jQuery

- 插件

- jQuery 制作插件

- 常用方法

- bind / on / click

- js-ajax-* 实现异步

- 全局body loading 为wj实现

- 根据 event.timeStamp 防抖

- 设置select 的默认值

- 图片放大

- 图片懒加载

- 文件异步下载 / 带百分比

- 文件异步上传 / 带百分比

- 拖拽上传文件

- 常用指令

- AJAX

- 全局 Ajax 事件处理器

- $().ajaxPrefilter ajax前置与后置监听

- $.get

- $.getJSON

- $.getScript

- $.post

- $.ajax

- $().load

- .serialize() / .serializeArray()

- DOM

- .addClass() / .removeClass()

- .hasClass() / .toggleClass()

- .attr() / .removeAttr()

- .prop() / .removeProp()

- .html() / .val() / .text()

- .data() / .removeData()

- .after() / .before()

- .append() / .appendTo()

- .prepend() / .prependTo()

- .clone()

- .detach() / .empty()

- .each() 遍历 jQuery 对象

- .get()

- ====== 元素选择 ======

- .eq() / .first() / .last()

- .filter() / .find() / .has()

- .next() / .prev()

- .parent() / .parents()

- CSS

- .css()

- .height() / .width()

- .innerHeight() / innerWidth()

- .outerHeight() / .outerWidth()

- .position()

- .scrollLeft() / .scrollTop()

- 动画 / 特效

- .animate()

- .delay() / .finish() / .stop()

- .fadeIn() / .fadeOut() / .fadeTo()

- .hide() / .show() / .toggle()

- .slideDown() / .slideUp() 滑动

- 浏览器事件

- .scroll()

- .resize()

- Event 对象

- event.currentTarget

- event.target

- event.data

- event.isDefaultPrevented()

- event.which 按键监听

- event.pageX / event.pageY

- event.preventDefault()

- event.stopPropagation()

- event.timeStamp

- event.result

- event.type

- event.key

- 事件监听

- .on()

- .one() 触发一次

- .trigger()

- .off() 移除事件

- 表单事件

- .blur() / .focus()

- .focusin() / .focusout() 支持冒泡

- .change()

- .select()

- .submit()

- 键盘事件

- .keydown() / .keypress()

- .keyup()

- 鼠标事件

- .click() / .dblclick()

- .contextmenu() 右键

- .hover()

- .mouseup() / .mousedown()

- .mouseenter() / .mouseleave() 鼠标进入 / 移开

- .mousemove() 移动

- .mouseout() / .mouseover() 冒泡移入/移除

- 工具类

- .grep() 过滤数组

- .map() 转为另一个数组

- .merge() 合并数组

- .each() 遍历数组和对象

- .inArray()

- ==== 数组 ====

- $.param / $().serialize / $().serializeArray()

- .extend() 合并对象

- ==== 对象 ====

- .trim() 去掉首尾空格

- .parseHTML() / .parseJSON() /.parseXML()

- ==== 字符串 ====

- .isArray()

- .isEmptyObject()

- .isFunction()

- .isNumeric()

- .isPlainObject()

- .type() 可区分 array 与 object

- ==== 类型判断 ====

- .now() 时间戳

- 函数 compose

- callbacks.add() 添加函数

- callbacks.empty() 清空函数

- callbacks.fire() 调用函数

- JavaScript

- 知识

- 同源限制

- 不同域跨窗口通讯

- typeof / instanceof

- JS 语法树

- 设计模式

- 严格模式

- 性能优化

- scrollHeight 等各中高度

- 技巧 / 场景

- onClickOutside 判断是否在严肃外

- clientX .pageX,screenX,offsetX 区别

- getBoundingClientRect 定位元素

- 下拉示例

- 自定义去除字符

- 打印时间戳

- 类型转换 黑魔法

- 只初始化一次

- 防抖 / 节流

- 动画

- 滑动删除

- ====== 技巧 ======

- this / bind / call /apply

- 函数式编程 / 柯里化

- compose 函数组合

- 原生面向对象写法

- 示例:canvas小球碰撞

- new 带prototype的函数

- ES5 实现继承

- 大文件断点续传

- ====== 场景 ======

- 插件

- JS 制作插件

- 实例:拖拽列表插件

- 图片/文件拖拽显示信息

- js 原生提示

- 手写签名

- JS 模块

- ES6 [推荐]

- CommonJS 模块

- ES6,7,8语法

- Promise

- Class

- Map / Set

- async / await

- 浏览器对象

- 浏览器环境概述

- window 对象

- Location 对象

- Navigator 对象

- Screen 对象

- XMLHttpRequest 异步请求

- console 对象

- URL 解析

- URL 的编码和解码

- URLSearchParams 对象转url参数

- 标准库 / 对象

- Object 对象

- Number 对象

- Array 数组

- String 对象

- Math 对象

- Date 对象

- RegExp 对象

- JSON 对象

- FormData 对象

- ArrayBuffer / Blob 对象

- File / FileList / FileReader 对象

- TextEncoder / TextDecoder

- DOM

- DOM,Node 接口

- Document 节点

- Element 等节点

- CSS 操作

- 事件

- EventTarget 事件通用接口

- Event 对象

- 鼠标事件

- 键盘事件

- 进度事件 - 加载外部资源

- 触摸

- 实例 手写

- PointerEvents 更通用的touch

- 拖拉事件

- 窗口事件

- 剪贴板事件

- GlobalEventHandlers 接口

- HTML 标签

- <a>

- <img>

- <input> 元素

- Web Api

- Fetch

- Response 对象

- Request 对象

- Headers 对象

- 实例

- POST 请求

- JSON 请求

- 上传文件

- 获取数据流-如图片

- 逐行处理文本文件

- 自定义请求 Request

- sessionStorage / localStorage

- Intersection Observer 元素可见判断

- PerformanceObserver 性能监听

- ResizeObserver 监听元素大小

- TextDecoder / TextEncoder

- Gamepad 游戏手柄

- geolocation 地理位置

- 网页可见性 状态监听

- Notification 系统通知

- 画中画API

- Pointer events 指针事件

- Vibration API 震动

- Audio API 声音

- Web Share API

- WebCodecs API 帧和音频块的访问

- Mutation Observer 监视 DOM 变动

- 数据类型

- TypeScript

- 技巧

- 声明文件

- 全局变量

- npm 包中使用

- UMD 库

- 模块插件

- tsconfig.json

- 语法

- 基础类型

- 装饰器(decorators)

- 命名空间

- 模块

- 高级类型

- 类型兼容性

- 接口

- 类

- 函数

- 泛型

- Record

- 高级类型

- ====== 基础 ======

- SVG

- 语法

- js 操作 SVG

- canvas

- 绘制矩形

- 绘制路径

- 绘制直线

- 绘制圆弧

- 绘制贝塞尔曲线

- 绘制文本

- 绘制图片

- 样式与颜色

- 状态的保存和恢复

- 变形

- 平移

- 旋转

- 变形矩阵

- 合成

- 裁剪路径

- 动画

- WebSocket

- 库

- websocketd

- socket.io

- WebGL

- twgljs 轻量级库

- WebRTC

- WebRTC 使用流程

- 概念

- 处理浏览器中的媒体

- 两种传输方式示例 视频 / 文本 / 流文本

- 需要信令通道

- 教程

- 媒体设备

- 对等连接入门

- 远程流

- 数据通道

- TURN服务器

- API 接口

- RTCPeerConnection

- getUserMedia

- 示例

- examples

- php 实现服务器与web端

- 捕获窗口

- 捕获摄像头

- 本地使用 RTCPeerConnection

- DataChannel

- 远程点对点

- 第三方库

- SimpleWebRTC [4.5k]

- webRTC.io [1.6k]

- ==== 视频聊天 ====

- peerjs 点对点链接

- 点对点传输文字

- 第三方项目

- p2p.chat

- im

- WebAssembly

- 示例

- hello-world go版

- SSE (EventSource)

- 示例

- Web Workers 多线程

- 示例

- 通用的异步 eval()

- Service Worker API

- PWA 提升WebApp

- Broadcast Channel 广播

- IndexedDB

- 库

- Dexie.js 封装 IndexedDb

- ZangoDB

- JsStore 带SQL语法

- lovefield 仿 SQL [6.8k]

- ====== 进阶 ======

- NodejS

- npm 插件

- mongoose 操作 mongodb

- sequelize 数据库orm

- pm2 启动 node

- nodemon 监控文件变化自动重启

- cookie-parser 设置 cookie

- Puppeteer 控制浏览器

- Robotjs 桌面自动化

- anyproxy 代理

- pkg 编译成二进制

- 文件操作

- 网络操作

- 进程管理

- Express 框架

- 模块化编程

- Koa web 框架

- Deno 代替node

- bun

- 命令

- bunfig.toml

- 接口

- API

- Bun APIs

- Web APIs

- Node Js

- ====== 后端 ======

- Vue

- 问题

- 运行网页,但是报缺少 Node 的相关库

- 技巧

- 异步加载

- 动画,与动画库的使用

- webpack 构建多页面

- vue3.0 语法

- reactive,ref,watch,watchEffect,computed

- 子组件

- TypeScript

- 性能优化

- 测试 Vitest

- 动画

- 依赖注入 Provide与Inject

- Suspense 异步加载组件

- directives 自定义指令

- 组合式函数 useXXX

- 插件

- vue 库

- axios 请求

- vue cli 3.0 配置

- qrcode.vue 二维码

- Vue-router

- vue-i18n

- VeeValidate

- vueuse

- 存储 useLocalStorage 等

- ref 的 各种undo,redo

- ====== State ======

- useActiveElement

- useDraggable

- useDropZone 可拖动到区域

- useElementBounding

- useElementSize width,height

- 元素可见性

- useMouseInElement

- useWindowScroll

- useWindowSize

- useTextareaAutosize 自动增高

- useTitle

- useUrlSearchParams url参数

- onClickOutside 元素外点击

- useFocus / useFocusWithin 元素是否激活

- ====== Elements ======

- useClipboard

- ColorMode 切换主题

- useEventListener

- useFileSystemAccess 文件信息

- useObjectUrl 查看文件内容

- useFullscreen

- useMediaControls 媒体内容

- usePermission 权限

- useWebNotification

- useWebWorker

- ====== Browser ======

- onKeyStroke 监听键盘

- onLongPress 长按时长

- useDevicesList 媒体设备

- useDisplayMedia 使用设备源

- useGeolocation 定位

- useInfiniteScroll 下拉滚动

- useKeyModifier 按键监听

- useMouse

- useNavigatorLanguage 语言

- useNetwork

- usePageLeave

- useSpeechRecognition 语音

- useTextSelection 选中文字

- ====== Sensors ======

- ====== Component ======

- useVirtualList 虚拟列表,高性能

- ======== 工具库 ========

- watchDeep 监听深度对象

- watchDebounced 防抖

- watchOnce 监听一次

- watchThrottled 节流

- useDebounceFn /useThrottleFn 防抖函数

- useEventBus 通知

- ====== watch ======

- useArrayDifference

- ====== Array ======

- useDateFormat 当前时间

- useTimeAgo 多久前

- ====== time ======

- useAsyncValidator 验证

- useChangeCase 单词切换

- useCookies

- useQRCode 二维码

- useSortable 拖拽排序

- ====== Integrations ======

- ====== 工具库 ======

- better-scroll 更好的无滚动条插件

- vue-infinite-scroll 下拉加载

- vue-infinite-loading 上拉刷新,功能强

- vue-lazyload 图片懒加载 -vue2.0

- Vue.Draggable 拖住div

- vue-fullpage

- form-generator 表单生成器[UI版]

- vue-form-making element-ui 可视化表单

- vue-cron Cron表达式组件

- vue-good-table 表单组件

- vxe-table

- skeletonreact 骨架屏

- ======== UI 库 ========

- vuex 状态管理

- 在多页面中使用

- 创建 store.js

- Pinia 状态管理

- pinia-plugin-persist-uni 适配 uni

- hello world 实例

- ======== 状态库 ========

- Nuxt 集成服务器渲染,ui框架等

- vue-element-admin

- ant-design

- d2-admin vue+ElementUI 后台框架

- vuetifyjs 37.4k

- 特性

- 别名

- 全局配置

- 字体图标

- i18n

- scss

- 主题

- 辅助类

- 组件

- v-spacer 空白弹框

- v-item-group

- v-hover 悬停事件

- v-list

- 指令

- v-ripple

- v-scroll

- ======== 框架 ========

- React

- 第三方库

- Shadcn UI 可定制UI 框架

- flowbite 基于 Tailwind UI

- ChatUI

- wasp 快速制作前后端

- motion.dev 动画库

- zustand 状态管理

- immer 优雅更新state对象

- lucide-react 图标库

- swr 请求库

- react-query 请求库

- date-fns 时间

- zod 验证

- react-hook-form

- react-hot-toast 通知9.9k

- React Flow 可视化流程节点

- 语法

- hook

- 自定义 hook

- useEffect

- useMemo 缓存计算结果

- useSyncExternalStore 获取外部数据

- useCallback

- useDeferredValue

- 组件

- StrictMode 严格模式

- Suspense 加载前的提示

- API

- 组合 vs 继承

- 状态提升

- 表单

- 列表 & Key

- 条件渲染

- 事件处理

- State

- 组件 & Props

- JSX

- Context 深层传递参数

- ref 更新不触发刷新

- Next.js

- Routing

- pages

- layout

- Routing

- Error Page

- Loading

- Link

- Parallel Routes

- Intercepting Routes 模弹窗路由

- layou 布局

- 环境变量

- API 路由

- Svelte

- 示例

- 编译为一个web Component

- Web Components

- 示例

- template 方式

- javascript 方式

- ====== 框架 ======

- 鸿蒙

- 安装

- 示例

- Hello World

- 目录说明

- resources 目录

- ArkTS 语言

- 组件

- 状态管理

- LocalStorage 页面级状态

- AppStorage 全局状态

- emitter 事件监听

- PersistentStorage 持久化

- Environment

- ASK UI 框架

- 布局

- 组件

- React Native

- 命令

- Codegen

- 常用库

- ignite 构建项目模版

- react-i18next 多语言

- react-devtools 调试

- date-fns 日期框架

- FlashList 高性能列表

- async-storage 持久化

- datetimepicker 时间选择器

- react-native-picker-select 原生弹窗选择器

- segmented-control tab 切换

- react-navigation 原生导航

- @react-navigation/bottom-tabs 底部导航栏

- @react-navigation/elements 标题栏

- react-native-doc-viewer 文档预览

- react-native-calendars 日历

- react-native-popup-menu 按钮菜单/底部菜单

- react-native-snap-carousel 切换图片

- react-native-keyboard-aware-scroll-view 输入框自动键盘滚动

- nativewind tailwind风格

- react-native-bottom-sheet 可拉动底部弹窗

- 鸿蒙

- 插件

- 鸿蒙官方插件

- 第三方库

- Electron 桌面应用

- 快速入门

- 技巧

- 内置模块

- app 模块

- BrowserWindow

- Menu 菜单

- globalShortcut (全局快捷键)

- Shell

- dialog 对话框

- tray 系统托盘

- webContents 渲染以及控制 web 页面

- ipcMain / ipcRenderer (进程间的通讯)

- clipboard 剪切板

- webview

- protocol 自定义协议

- desktopCapturer 获取其他软件信息

- 常用包

- electron-settings 设置管理器

- electron-log

- electron-builder 打包[推荐]

- electron-packager 打包

- electron-updater 升级

- electron-store 以文件形式缓存配置

- menubar 托盘菜单栏

- photon 桌面 UI 构建

- React Desktop macOS和Windows的UI工具包

- chrome-tabs

- xel 界面ui

- electron-util 常用包

- electronic-vue

- wails go实现的跨平台

- Runtime

- Events

- Log

- window 窗口

- Dialog 对话框

- Menu 菜单

- Browser 浏览器

- Clipboard 剪贴板

- Screen

- app 参数

- tauri 桌面开发

- 系统APi

- weex 跨平台vue 开发

- weex-ui 第三方 ui 库

- wexx-bindingx 动画效果

- wails go版pc端

- Taro 小程序

- 技巧

- 配置

- 路由

- 编译优化

- NutUI UI组件

- subPackages 分包

- 组件库

- CustomWrapper 用于动态更新

- PageContainer 半屏页面

- RootPortal 弹窗

- ScrollView 滚动

- Swiper/SwiperItem

- Vue

- 生成周期

- NutUI 基于vueUI库

- uniapp

- 插件 / 资源

- [通用] 更好的下拉刷新,上拉加载

- [app] 全量更新 app-简单

- [app] 可增量更新

- 登录/注册模板(含微信等第三方登录)

- 导航栏

- uni-form 表单校验

- combox 自动完成

- uni-data-checkbox

- uni-data-picker

- uni-loadmore 上拉加载更多

- uni-row 布局

- uni-dateformat 日期格式化,倒计时

- uni-file-picker 文件上传

- uni-search-bar 搜索栏

- uni-segmented-control 分段器

- UI 框架

- uni-框架

- ColorUI-UniApp

- uView UI 更多功能

- 快速入门

- 设计图尺寸

- 设置开发/生产模式

- 设置 scss 等样式

- 生命周期

- 组件/标签的变化

- template 与 block

- NPM支持

- 资源路径

- css 相关

- js 导出模块

- 使用 TypeScript

- 组件管理

- 事件处理器

- vuex

- 配置

- pages.json

- easycom

- package.json

- uni.scss

- App.vue

- main.js

- 生命周期

- 应用生命周期

- 页面生命周期

- 组件生命周期

- Vue

- 事件处理器

- 表单使用 v-model

- 组件的props

- 组件的ref

- 组件的.sync 子组件prop通知父组件

- 原生组件

- button

- page-meta

- navigation-bar

- custom-tab-bar

- open-data

- 运营服务

- 统一推送uniPush

- 运营统计

- 制作统一发行页面

- API

- 媒体

- uni.compressImage 压缩图片

- 设备

- 陀螺仪

- 系统信息

- 网络状态

- 罗盘

- 加速度计

- 拨打电话

- 扫码

- 剪贴板

- 屏幕亮度

- 手机振动

- 蓝牙

- 生物认证

- 键盘

- 界面

- 弹出菜单

- 设置导航条

- 设置 tabBar

- 背景/下拉背景

- 动画

- 滚动页面

- 网络字体

- 下拉刷新

- 节点信息

- 节点布局相交状态

- 文件

- 绘画

- 第三方服务

- 获取服务供应商

- 登录

- 检测是否登录

- 微信登录

- 信息获取

- 获取手机号

- 手机号一键登录

- 支付

- 推送

- 模板消息-小程序

- 授权

- 小程序设置界面

- 收货地址

- 打开其他小程序

- 模版消息

- 订阅消息

- 小程序更新

- App 更新

- 调试

- 统计 - uni 对程序的统计

- 广告

- 页面通讯 / 全局事件监听

- 公用模块 / 全局变量

- uni_modules

- datacom

- 自动化测试

- wexx / nvue

- HTML5+

- 国际化

- 微信小程序

- ====== 平台相关 ======

- webpack

- loader 插件

- babel-loader ES6 转为 ES5等

- html-loader

- css-loader

- postcss-loader 对 css 进行后处理

- less-loader

- url-loader 过小生成 base64位图片

- file-loader 引入图片

- image-webpack-loader 图片压缩

- 引入模块-并对模板赋值

- esbuild

- Api

- Build API

- 高级配置

- 语法

- gulpjs 构建工具

- 快速入门

- 语法

- 常用插件

- css 插件

- js 插件

- 图片 插件

- 自动刷新页面

- 示例

- 编译sass

- 监听 css变化

- 监听 文件变化,刷新页面

- 多页面示例

- 模版

- rollup 0配置打包脚本

- Rspack 基于Rust,兼容webpack

- lerna 管理包含多个软件包

- 命令

- 快速入门

- vite

- 功能

- 命令行

- vite

- 插件

- 兼容传统浏览器插件

- 示例

- 普通 html, 支持 import

- ====== 构建工具 ======

- npm

- npm 插件制作发布

- cnpm - 淘宝的 npm 镜像

- npx

- yarn

- 命令

- plugin

- .yarnrc.yml

- pnpm

- 命令选项

- Bower 浏览器管理插件

- ====== 包管理 ======

- SEO 优化

- ====== 性能与优化 ======

- vConsole

- 远程调试移动设备网页

- chil 远程调试网页

- 远程调试 Android 设备网页

- selenium 自动测试

- selenium IDE

- selenium Python

- 常用技巧

- 定位 元素 / 一组元素

- 控制浏览器操作

- WebDriver常用方法

- 鼠标事件

- 键盘事件

- 获取断言信息

- 设置元素等待 -等待某条件成立后在执行

- 多表单切换

- 多窗口切换

- 警告框处理

- 下拉框选择

- 文件上传

- cookie操作

- 调用JavaScript代码

- 窗口截图

- 关闭浏览器

- Chrome headless 无界面模式

- CukeTest 可测桌面应用

- 语法

- Tree 结构的选择

- 数据驱动测试用例

- 模型管理器

- 批量运行工具

- 常用工具函数

- Cucumber API

- this.attach 在执行后进行截图

- 每个场景后截图至报告

- 模拟桌面操作API

- 模拟 Ctrl+A

- 禁用中文输入法

- ====== 使用工具 ======

- 谷歌浏览器插件

- 概念

- manifest.json

- popup

- background

- content

- plasmo 浏览器插件框架

- 示例

- Popup

- options 选项页

- newtab 新标签

- background

- messaging 通信

- content

- Tab pages

- storage

- Env

- package 转 manifest

- Assets

- Icon

- lang

- 谷歌接口

- extension

- browserAction

- tabs

- contextMenus

- notifications

- omnibox

- 互相通信概览

- 长连接和短连接

- windows

- storage

- webRequest

- cookies

- runtime 插件相关

- manifest

- ====== 浏览器插件======

- chrome

- puppeteer js控制chrome

- DevTools protocol 通过websocket控制

- 命令行

- go 版本

- ====== chrome 控制 ======

- XPath

- ====== 文本生成图 ======

- plantuml

- mermaid.js

- 软件

- jetbrains / Intellij IDEA

- 常用插件

- Git Commit Message Helper

- Chinese (Simplified) 中文组件

- Php Inspections (EA Extended)

- redis simple -redis 客户端

- plantuml-integration uml 绘制

- 制作插件

- 连接远程docker

- 配置vagrant虚拟机

- 保存监听 eslint

- uni-app 代码提示

- docker 使用 phpstorm/php-71-apache-xdebug

- php 本地debug / 远程debug

- php 代码检测

- grumphp 限制 commit 提交

- vs code

- 常用插件

- C++ 配置

- Go 配置

- Qt 配置

- php 调试

- 同步设置

- 插件制作

- 单元测试

- i10n

- 发布插件

- 扩展工作台

- 数据储存

- package.json 清单

- visual studio

- 使用 Clang/LLVM

- 运行Qt

- 内网部署vs及插件

- 插件

- ReSharper C++

- Clang Power Tools

- Sublime Text配置

- github

- gource 通过 git 生成 动画

- thefuck 出现错误使用 fuck

- tldr 简化 man 函数

- postman

- Apache JMeter 并发测试工具

- Chrome

- 控制台

- Apche Directory Studio - LDAP软件

- sokit 端口监听 转发. socket 测试工具

- wireshark 抓包工具

- Ventoy 多系统合一启动盘制作工具

- UserLAnd 手机安装linux

- termux 手机安装 linux

- sharemouse 跨系统操作

- Microsoft Garage Mouse 多windows跨键盘

- syncthing 分布式同步

- D盾

- openArk

- dbeaver 跨平台数据库

- 搭建 shandowsocks

- google云 搭建

- 亚马逊云 搭建

- 终端走代理

- 一键 ss 脚本

- ⬇⬇⬇⬇⬇ 无界面软件 ⬇⬇⬇⬇⬇⬇

- sqlmap 防sql 注入的测试

- scrcpy 手机投屏

- sftpgo 跨平台 ftp

- frp 内网穿透

- AWS 亚马逊

- 小米路由AX3600

- upx 压缩可执行文件

- firebase 赛博菩萨软件

- 安卓

- adb

- emulator 虚拟器

- 安卓抓包

- MAC

- php 环境配置 2.0版

- pear / pecl 安装

- Mac 配置 Python 和Python3

- 配置 Oh My Zsh+ iTerm2

- iTerm2 自动登陆 ssh

- 配置 Vim

- brew

- 创建 brew 包

- MAME 街机模拟器

- php-osx mac 安装php

- 破解 wifi

- iOS注册美区Apple ID教程

- Window

- 常见问题

- 打不开微软商店

- cmd 命令

- cmd 运用场景

- 复制目录

- 删除目录下的所有文件

- < 交互时可自动输入

- 查看端口占用的pid

- 当前目录管理员身份运行

- 批处理命令

- echo / rem 注释

- pause 暂停

- call 调用其他 bat

- goto

- set 设置变量

- 获取命令行参数

- 常用命令

- tasklist 查看进程

- taskkill 进程操作

- ipconfig

- nslookup 域名解析

- netstat

- route 路由信息

- arp 查看ip使用情况

- findstr

- robocopy

- SpaceSniffer 检查磁盘文件暂用大小

- choco win包管理神器

- 创建 choco 包

- 实例

- nupkg 常用函数

- WSL 2 -方便win docker

- Sysinternals 微软工具箱

- Autologon 免密登录

- Psexec 远程执行工具

- Autoruns 查看启动项

- AdExplorer / AdInsight AD与LDAP查看器

- BgInfo 电脑信息生成到桌面

- LogonSessions 列出登录时间

- PsInfo 系统信息

- PsKill 终止(本地或远程)进程

- PsPing Tcp ping

- PsLoggedOn 显示登录的用户

- PsPasswd 更改本地或远程的密码

- PsShutdown 关闭或重启(本地或远程)电脑

- RDCMan 批量管理远程

- TcpView 列出套接字

- ZoomIt 屏幕缩放

- scoop 包管理器

- 添加ftp 服务

- vcpkg c++包管理器

- 升级 TLS

- clumsy 模拟不稳定网络环境

- Dependencies 查看 exe 依赖的dll

- portableapps 软件装U盘

- mobaXterm 类Xshell

- mouse without borders 共享键鼠

- IIS

- dumpbin 类似 linux 的 ldd

- geek 卸载工具

- 配置内外网双网卡

- YY-Thunks 现代应用兼容低版本

- Win11Debloat win11移除无用软件

- CFF Explorer

- Linux

- 知识碎片

- profile 与 bashrc

- /etc/init.d/functions 公共函数

- 实例

- &>file、2>&1、1>&2、/dev/null

- 管道和重定向

- 守护进程脚本

- 几个重要的信号

- cli a-z 常用命令注解

- 选项优先级

- 使用场景

- 创建用户,给root权限

- 设置服务器时间

- [自制] 批量操作多节点的脚本

- 引用环境变量替换文字模版

- umount 挂载硬盘

- 内核版本/系统版本信息

- 设置静态 IP

- 常用命令

- 文本 / 文件 / 目录

- egrep = grep -E 查看文件内容

- grep 查看文件内容

- awk 对文本每行处理

- sed 处理文本文件

- xargs 多行转换

- find 文件查找

- locate 比find 更快的索引

- wc 统计文字

- tr 替换与清除

- cut 按列切分

- tee

- 守护进程

- systemd 定时器

- systemctl 守护进程

- systemctl

- Unit.server 配置

- 实例

- 讲解 sshd 配置

- 实例 配置 go-web

- Type=forking 的使用

- journalctl 日志管理

- systemd-analyze 启动耗时

- hostnamectl 主机信息

- localectl 查看本地化设置

- timedatectl 查看当前时区设置

- loginctl 查看用户信息

- goreman 服务管理 [神器][golang]

- supervisor [python]

- supervisord [golang][带GUI]

- chkconfig 开启启动管理

- 标准 init.d 模版

- httpd 开启启动

- 调试工具

- strace 调试脚本

- pstack 跟踪进程栈

- perf 性能分析工具

- stress 压力测试

- ab 压测工具

- ldd 查看执行文件的依赖

- readelf 动态库的真实版本

- patchelf 强制指定LB_LIBRARY_PATH

- tcpdump

- gdb 调试利器

- lsof 查看当前系统文件

- ss 网络端口查询

- free 内存情况

- iotop 查看进程 IO

- iftop 网络 IO 监控

- tc 模拟弱网

- 运维工具

- ansible 批量执行多服务器

- awx UI管理工具

- expect - 自动交互脚本

- envsubst 替换模版中的环境变量

- top / uptime

- sshpass 非交互密码登录

- bash-completion 命令补全

- 查看硬件信息

- lscpu 显示cpu型号

- arch 查看架构

- uname 查看系统版本

- cat /proc/meminfo 查看内存信息

- lsb_release 系统信息

- arch cpu架构

- ulimit

- 网络工具

- nmcli 配置静态网络

- nmap 端口扫描

- 磁盘管理

- df 磁盘使用情况

- du 统计文件占用

- 管理用户/组

- useradd

- usermod

- userdel

- groups 查看

- groupadd

- groupmod

- groupdel

- passwd

- openssh

- ssh openssh-client包

- 客户端配置文件

- sshd openssh-server包

- openssl 使用 openssl 包

- 实例

- 服务器证书 .key 与 .pem

- 客户端证书

- 同时生成服务端与客户端证书

- 登录方式

- ssh-keygen 秘钥登录

- ssh-agent / ssh-add 秘钥记住密码

- 证书登录

- 端口转发

- scp

- rsync 增量同步

- sftp

- gcc

- 静态库

- 动态库(共享库)

- 安全

- firewall-cmd 防火墙

- iptables

- asd 内存硬盘

- ln

- tar

- diff

- watch

- patch

- Curl

- wget

- Vim

- Tmux

- NFS 文件共享

- ftp

- logrotate linux 日志切割

- NFS 网络文件

- manpages-zh 中文man

- Bash 脚本

- 快速入门

- 知识点

- $()与反引号区别

- 检查返回值

- !$ / !*

- shell替换上一条命名的变量

- bash 最简单 kv 数据库

- echo / printf / 快捷键

- Bash 的模式扩展

- 引号和转义

- 变量

- 常见变量

- 字符串操作

- 算术运算

- 参数

- getopts Bash内置

- getopt 基本也自带

- env / shift / exit

- read 用户输入值

- 条件判断

- select 菜单选择

- 循环

- 数组循环

- 花括号迭代

- seq 设置起始增量

- 函数

- 数组

- set 命令

- 脚本调用堆栈

- mktemp 命令,trap 命令

- Bash 启动环境

- 命令提示符

- 颜色

- 第三方脚本

- trash.sh 删除进回车站

- centos 7

- 安装 gui

- yum

- 切换 yum 源

- 建立 yum 仓库